# Technische Universität München Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Integrierte Systeme

# **Dissertation**

# A Network Processor Architecture with Application-Optimized Reconfigurable Processing Paths (FlexPath NP)

Dipl.-Ing. Rainer Ohlendorf

Munich, September 28th, 2010

# Technische Universität München Lehrstuhl für Integrierte Systeme

# A Network Processor Architecture with Application-Optimized Reconfigurable Processing Paths (FlexPath NP)

### **Rainer Ohlendorf**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Eckehard Steinbach

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. sc.techn. Andreas Herkersdorf

- 2. Univ.-Prof. Dr.-Ing. Erik Maehle, Universität zu Lübeck

Die Dissertation wurde am 28. September 2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 1. Juli 2011 angenommen.

#### Erklärung

Ich erkläre an Eides statt, dass ich die der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Promotionsprüfung vorgelegte Arbeit mit dem Titel:

A Network Processor Architecture with Application-Optimized Reconfigurable Processing Paths (FlexPath NP)

am Lehrstuhl für Integrierte Systeme unter Anleitung und Betreuung durch Prof. Dr. sc.techn. Andreas Herkersdorf ohne sonstige Hilfe erstellt und bei der Abfassung nur die gemäß § 6 Abs. 5 angegebenen Hilfsmittel benutzt habe.

- (✓) Ich habe die Dissertation in dieser oder ähnlicher Form in keinem anderen Prüfungsverfahren als Prüfungsleistung vorgelegt.

- ( ) Die vollständige Dissertation wurde in ... veröffentlicht. Die Fakultät für Elektrotechnik und Informationstechnik hat der Vorveröffentlichung zugestimmt.

- (√) Ich habe den angestrebten Doktorgrad noch nicht erworben und bin nicht in einem früheren Promotionsverfahren für den angestrebten Doktorgrad endgültig gescheitert.

- ( ) Ich habe bereits am ... bei der Fakultät für ... der Hochschule ... unter Vorlage einer Dissertation mit dem Thema ... die Zulassung zur Promotion beantragt mit dem Ergebnis: ...

Die Promotionsordnung der Technischen Universität München vom 1.8.2001 in der Fassung der 8. Änderungssatzung vom 22.12.2009 ist mir bekannt.

| München, den 28. September 2010 |                    |

|---------------------------------|--------------------|

| ·                               | (Rainer Ohlendorf) |

## **Acknowledgments**

At first, I would like to thank Prof. Andreas Herkersdorf for having given me the opportunity to work on such an interesting research project under his guidance. The past six years at the Institute for Integrated Systems at TUM were a great chance for me to broaden my knowledge based on my initial course of studies and have provided me with valuable experiences through both the research work and the frequent interaction with students from all over the world. In addition, I would like to thank Prof. Erik Maehle from the University of Lübeck for his interest in this topic and for acting as my secondary examiner on the doctoral examination commission.

At the institute, my foremost thanks is devoted to Dr. Thomas Wild, who - as acting head of the networking research activities - was always a prime contact person and counselor for the discussion of viable conceptual alternatives and research direction. His detailed feedback concerning the structure of the dissertation and assistance in finding the right line of arguments greatly helped me to improve the presentation of the achieved contributions. For the more technical aspects of the work, I have to thank my officemate and FlexPath project partner Michael Meitinger for the frequent and fruitful discussions, in which we were able to solve many challenges to our mutual benefit. Also the co-operation with Daniel Llorente, who designed the SmartMem DMA engine next door, has to be appreciatively mentioned.

Further important help came from Johannes Zeppenfeld, who has contributed with his computer science background in developing sound simulation models, especially during the development and evaluation of the HDGA classification algorithm. I have learned quite a lot in our discussions and could significantly expand my C/C++ programming skills. Christopher Claus was of great help in resolving FPGA-related problems as the institute's expert in the Xilinx tool chain. Finally, I would like to mention the following current and previous colleagues at the institute, who have all contributed to a very pleasant working atmosphere: Felix Miller, Gregor Walla, Roman Plyaskin, Stefan Wallentowitz, Michael Feilen, Prof. Walter Stechele, Doris Zeller, Verena Draga, Holm Rauchfuss, Robert Hartl and Dr. Paul Zuber.

Finally, I would also like to thank my family for their support, which was also an important factor in being able to successfully complete this thesis.

# **Table of Contents**

| Tak | ole of Con | tents                                                    | 9   |

|-----|------------|----------------------------------------------------------|-----|

| Sui | mmary of   | the Thesis                                               | 13  |

| Zus | sammenfa   | ssung der Arbeit                                         | 14  |

| 1.  | Introduc   | tion                                                     | 15  |

| 2.  | State of   | the Art                                                  | 23  |

| 2   | 2.1. Net   | twork Processors                                         | 25  |

|     | 2.1.1.     | Commercial Network Processor Architectures               | 25  |

|     | 2.1.2.     | Academic Network Processor Projects                      | 29  |

|     | 2.1.3.     | Conclusions                                              |     |

| 2   | 2.2. Net   | tworking Applications                                    | 37  |

|     | 2.2.1.     | IP Forwarding                                            | 37  |

|     | 2.2.2.     | QoS Mechanisms                                           | 37  |

|     | 2.2.3.     | Security Applications                                    | 38  |

|     | 2.2.4.     | Multimedia Applications                                  | 40  |

|     | 2.2.5.     | Mobile Networks                                          | 42  |

|     | 2.2.6.     | Carrier-grade Ethernet and Internet Backbone Evolution   | 45  |

|     | 2.2.7.     | Conclusions                                              | 46  |

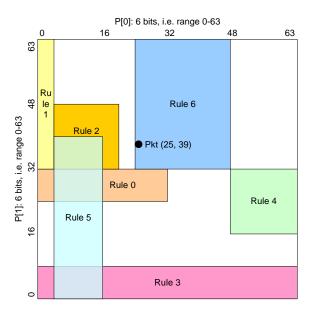

| 2   | 2.3. Pad   | cket Classification                                      | 49  |

|     | 2.3.1.     | Single-Field Classification                              | 49  |

|     | 2.3.2.     | Multi-Field Classification                               | 56  |

|     | 2.3.3.     | Packet Classification and Logic Minimization             | 69  |

|     | 2.3.4.     | Conclusions                                              | 70  |

| 2   | 2.4. Mu    | lti-Processor Load Balancing                             | 73  |

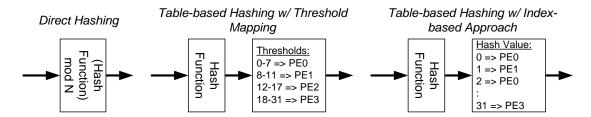

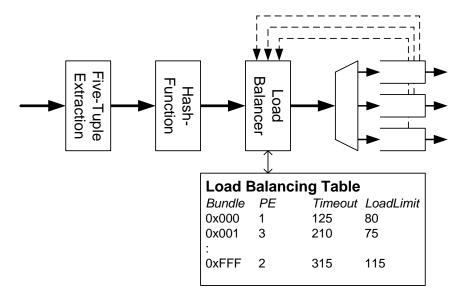

|     | 2.4.1.     | Hashing-based Load Balancing Schemes                     | 73  |

|     | 2.4.2.     | Hash-based Load Balancing with Overload Spraying         | 74  |

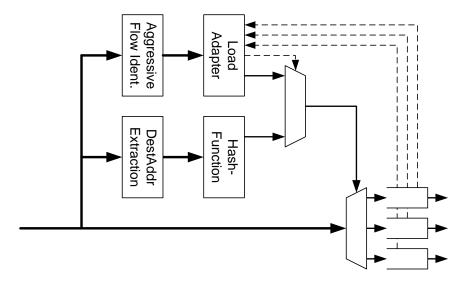

|     | 2.4.3.     | Adaptive HRW Hashing (AHH)                               | 75  |

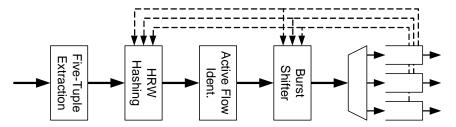

|     | 2.4.4.     | Adaptive Burst Shifting (ABS)                            | 75  |

|     | 2.4.5.     | Hashing Adapted by Burst Shifting (HABS)                 | 76  |

|     | 2.4.6.     | Conclusions                                              | 77  |

| 3.  | FlexPath   | n NP Architecture                                        | 79  |

| 3   | 3.1. Mo    | tivation and Problem Formulation                         | 79  |

| 3   | 3.2. Flex  | xPath NP Concept                                         | 83  |

| 3   | 3.3. Coi   | ncept Evaluation                                         | 89  |

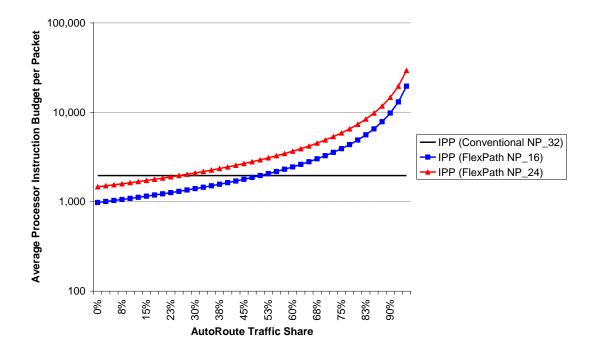

|     | 3.3.1.     | Analytical Evaluation of AutoRoute in FlexPath NP        |     |

|     | 3.3.2.     | Simulative Evaluation of Hardware-Offload in FlexPath NP |     |

| 3   | 3.4. Coi   | nclusions                                                | 105 |

| 4.  | Concent    | t and Implementation of Path Dispatcher                  | 107 |

|     | -          | roduction and Problem Formulation                        | 107 |

|     |            |                                                          |     |

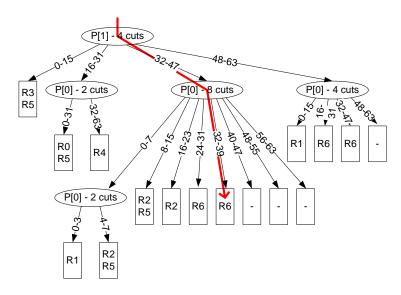

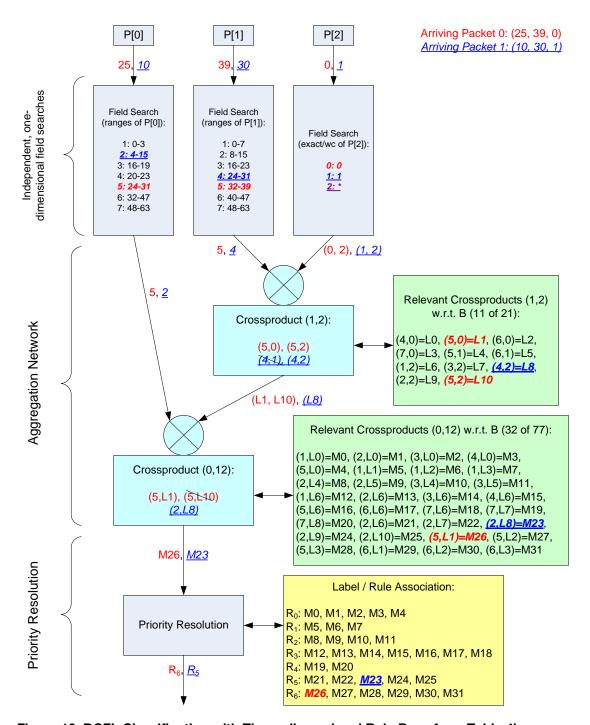

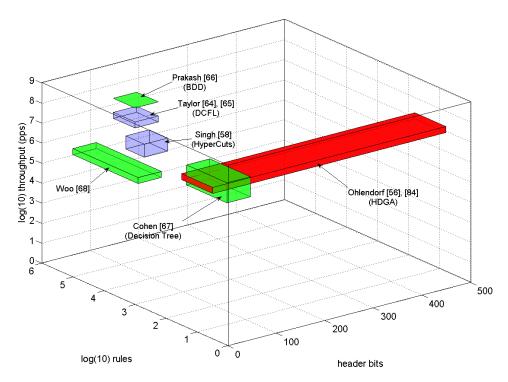

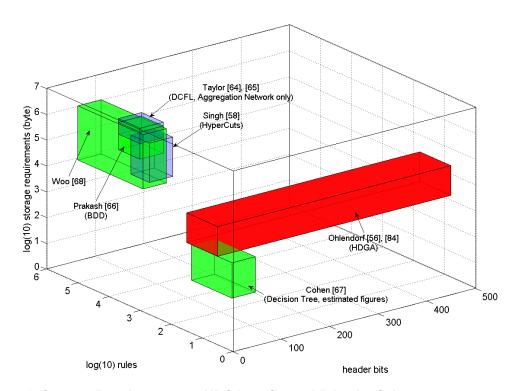

|    | 4.2. The  | Heterogeneous Decision Graph Algorithm (HDGA)                | 113   |

|----|-----------|--------------------------------------------------------------|-------|

|    | 4.2.1.    | Formulation of Rule Base using Boolean Variables             | 114   |

|    | 4.2.2.    | Matrix Representation of Rule Base and Pre-Processing        | 116   |

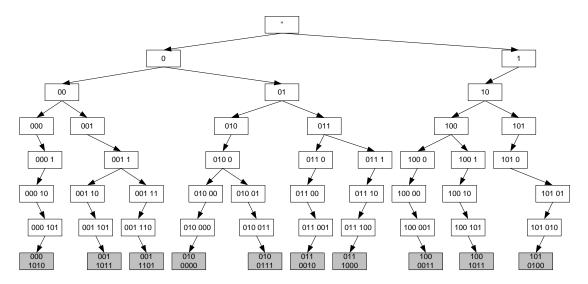

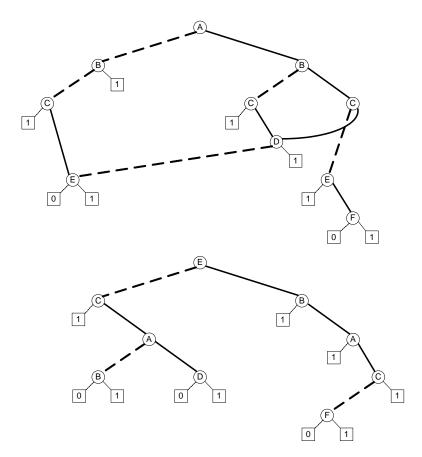

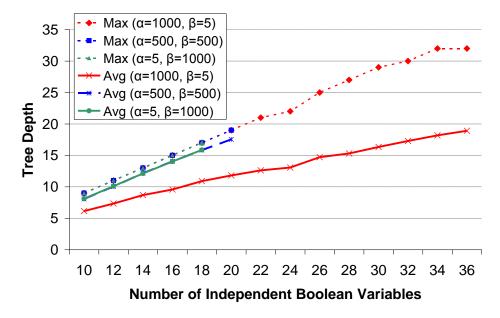

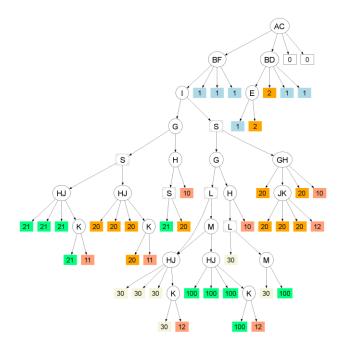

|    | 4.2.3.    | Construction of a Binary Decision Tree                       | 117   |

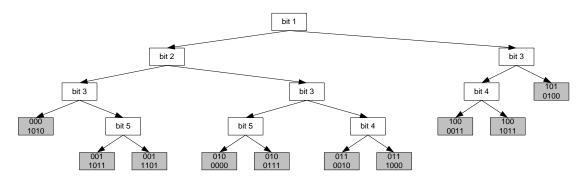

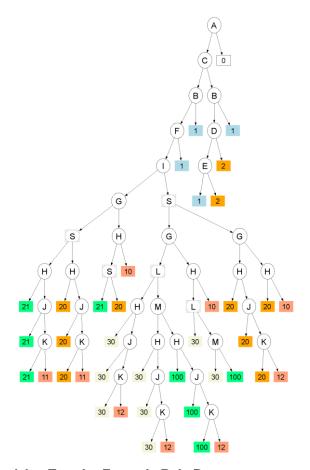

|    | 4.2.4.    | Transforming the Tree into the HDGA Decision Graph           | 125   |

|    | 4.2.5.    | Updates of the Rule Base and HDGA Data Structures            | 127   |

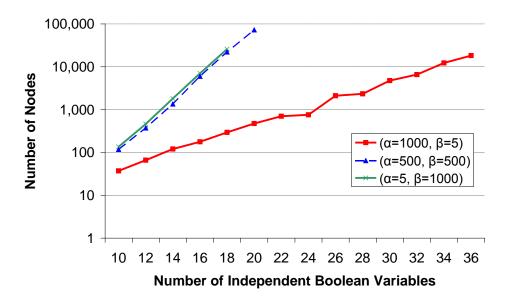

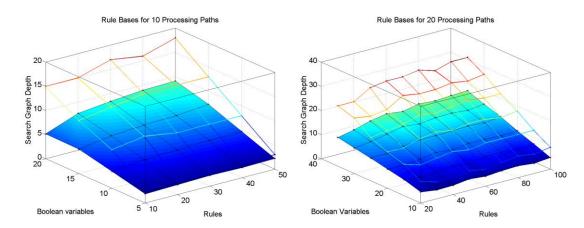

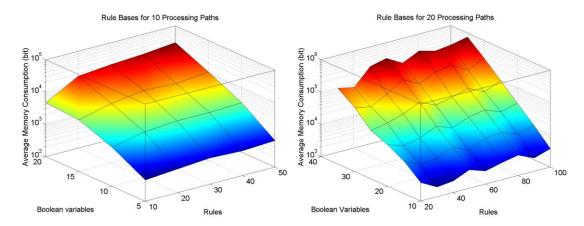

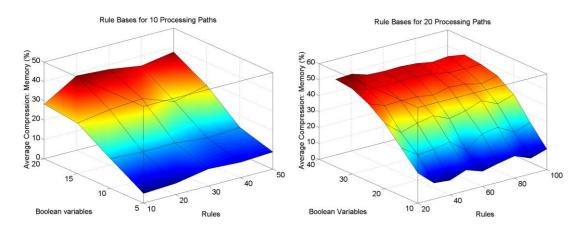

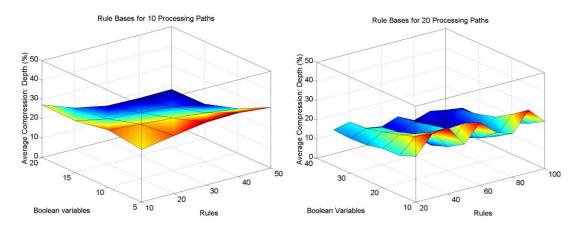

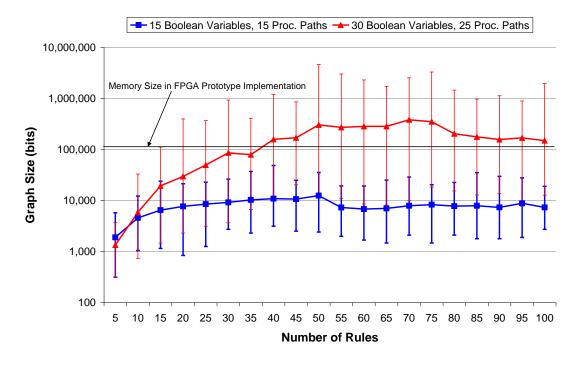

|    | 4.3. HD0  | GA Performance and Scalability                               | 129   |

|    | 4.4. Imp  | lementation Issues                                           | 133   |

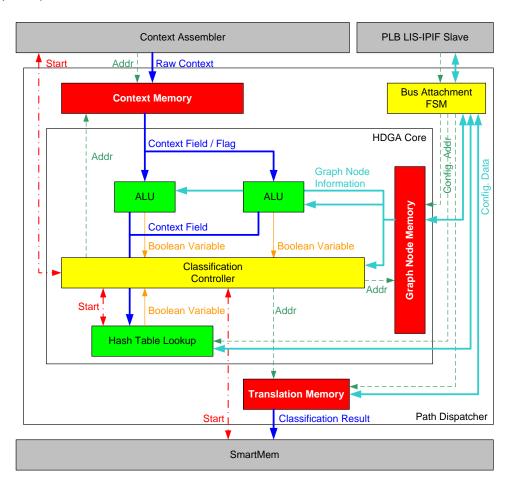

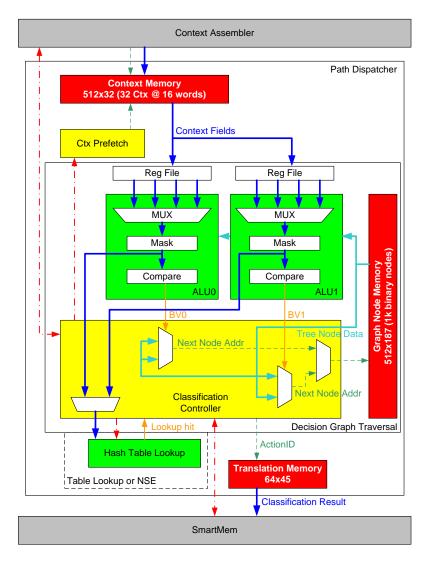

|    | 4.4.1.    | Path Dispatcher Interfaces                                   | 133   |

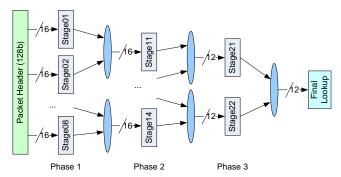

|    | 4.4.2.    | Design Space Exploration for HDGA Implementation             | 135   |

|    | 4.4.3.    | FPGA Implementation Results                                  | 145   |

|    | 4.5. Cor  | nclusions                                                    | 147   |

| 5. | Multi-Pro | ocessor Load Balancing in FlexPath NP                        | 149   |

|    |           | oduction                                                     |       |

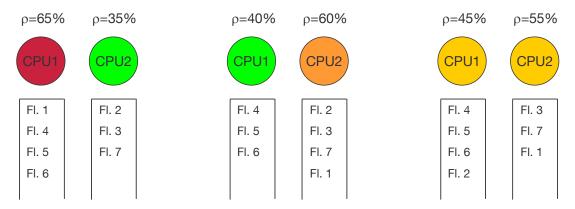

|    | 5.2. Loa  | d Balancing Strategies for Different Application Classes     | 151   |

|    | 5.2.1.    | Stateless Network Processing Applications                    | 151   |

|    | 5.2.2.    | Stateful Network Processing Applications                     | 153   |

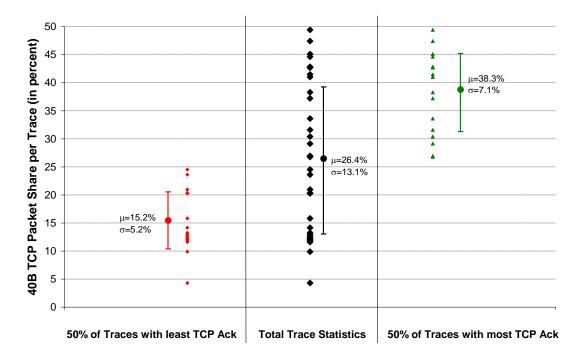

|    | 5.2.3.    | Combination of Stateless and Stateful Networking Application | າຣ158 |

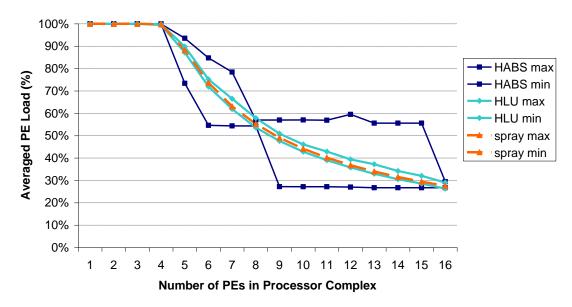

|    | 5.3. Fun  | ctional Simulation of Load Balancing Techniques              | 159   |

|    | 5.3.1.    | Simulation Model                                             | 159   |

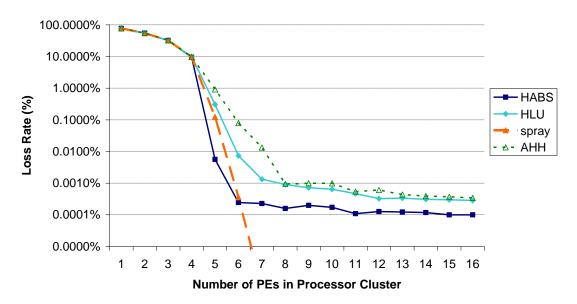

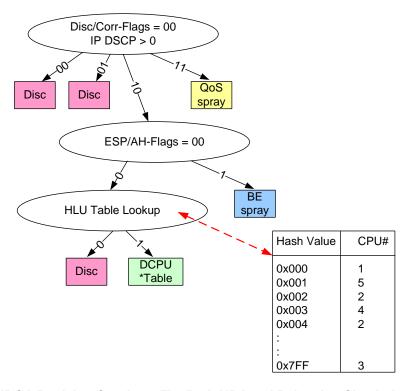

|    | 5.3.2.    | Individual Performance of Load Balancing Techniques          | 162   |

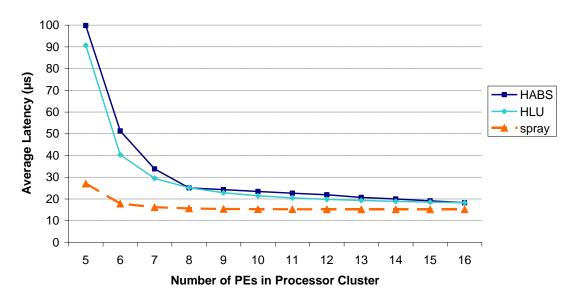

|    | 5.3.3.    | Performance of S&H Load Balancing                            | 167   |

|    | 5.4. Cor  | nclusions                                                    | 173   |

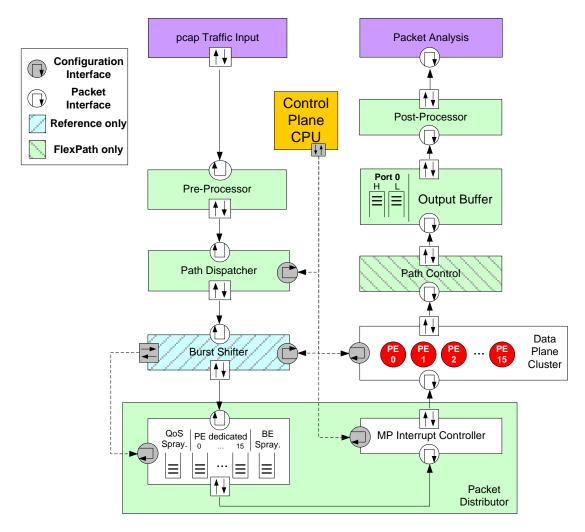

| 6. | FlexPath  | NP Demonstrator                                              | 175   |

| •  |           | nonstrator Goals and Platform                                |       |

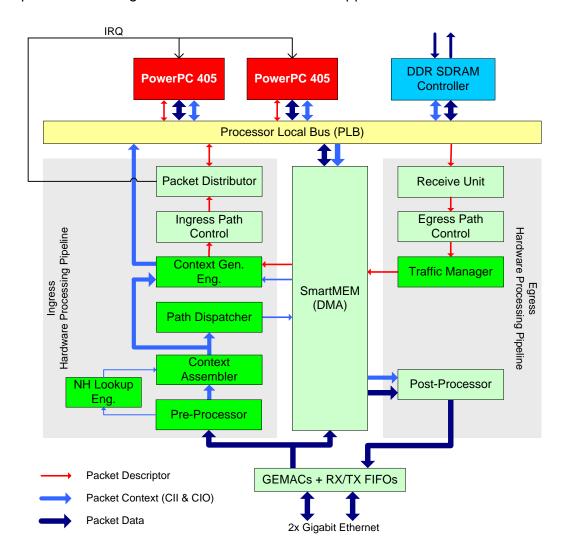

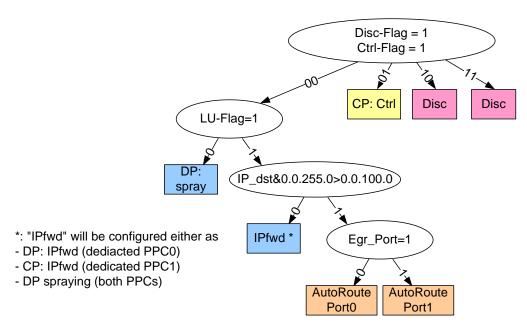

|    |           | Path NP System Overview                                      |       |

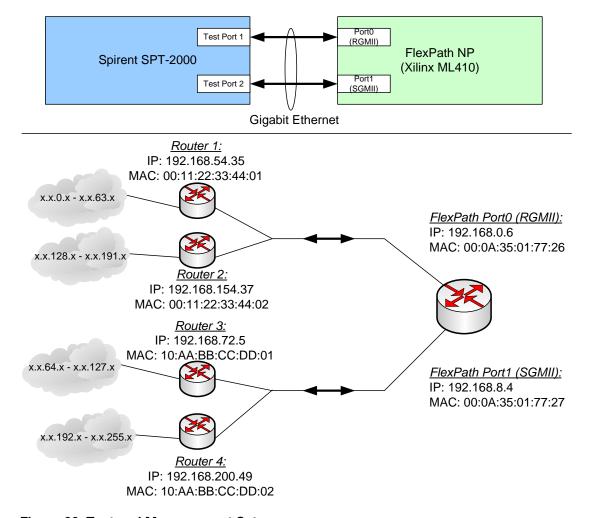

|    |           | asurement Setup                                              |       |

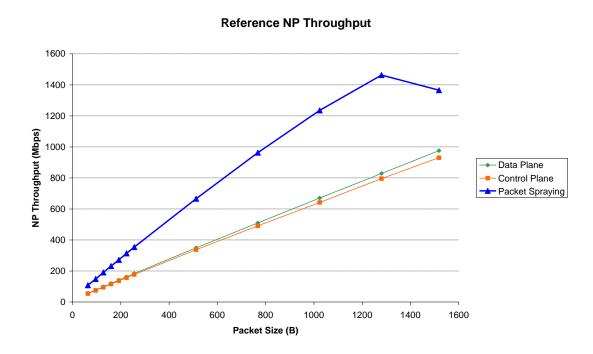

|    |           | cessor-centric Reference Measurements                        |       |

|    |           | dware-offload Aspects of FlexPath NP                         |       |

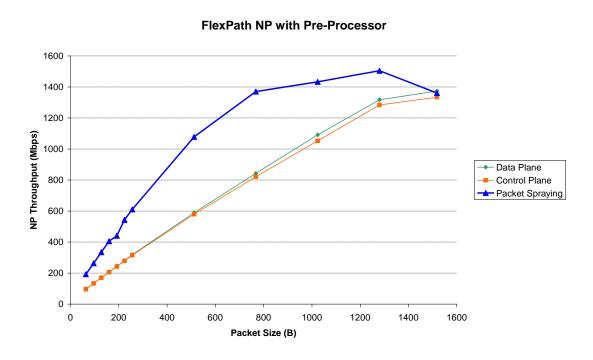

|    | 6.5.1.    | Forwarding Performance Using Pre-Processor                   |       |

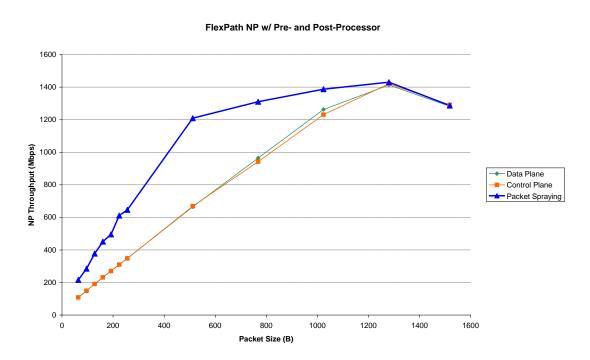

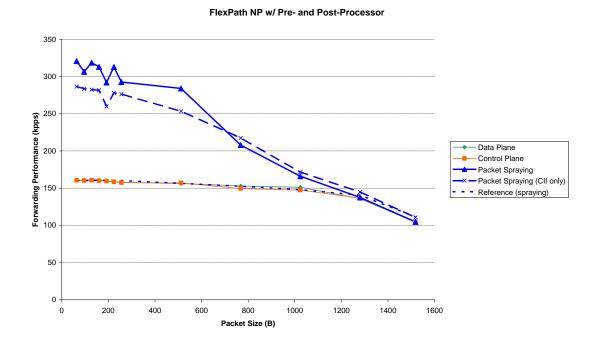

|    | 6.5.2.    | Forwarding Performance Using Pre- and Post-Processors        |       |

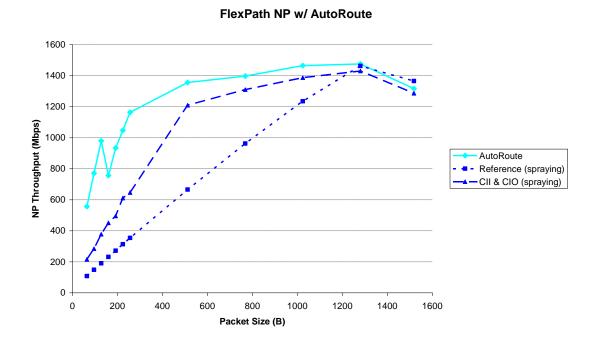

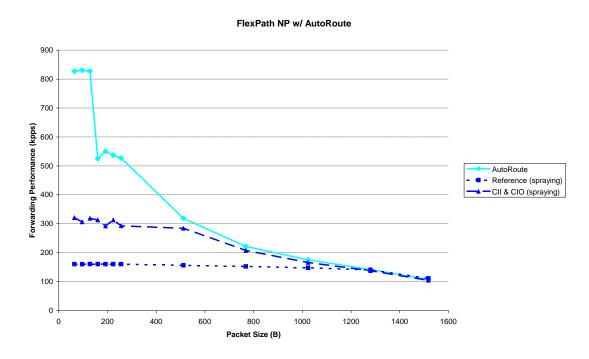

|    | 6.5.3.    | Forwarding Performance Using AutoRoute                       |       |

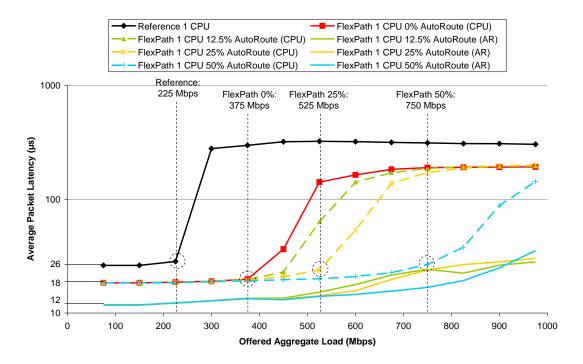

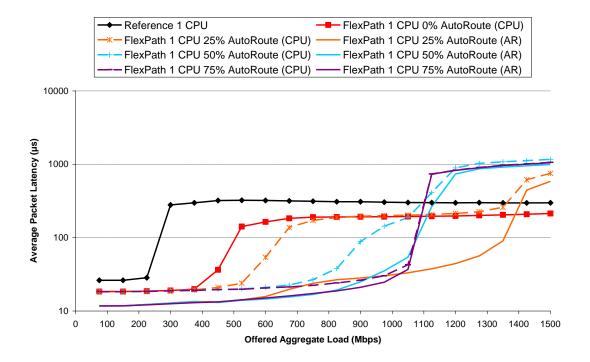

|    | 6.5.4.    | Packet Latencies                                             | 196   |

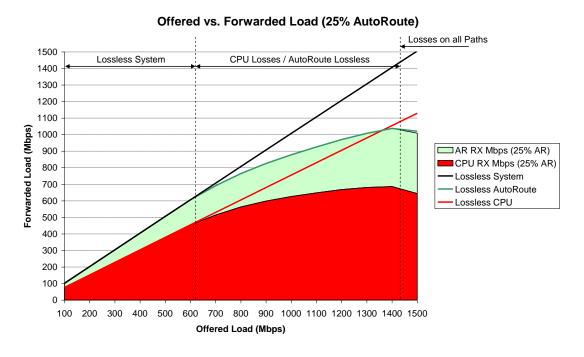

|    | 6.5.5.    | Packet Loss                                                  | 199   |

|    | 6.6. Loa  | d Balancing Algorithms on FlexPath NP                        | 201   |

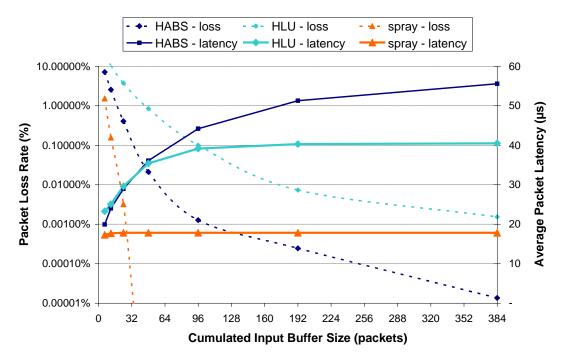

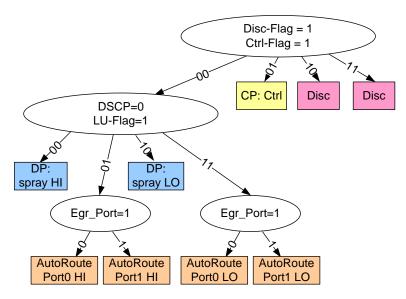

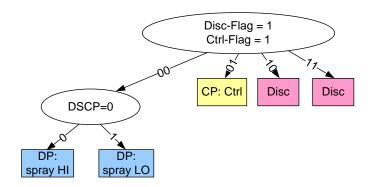

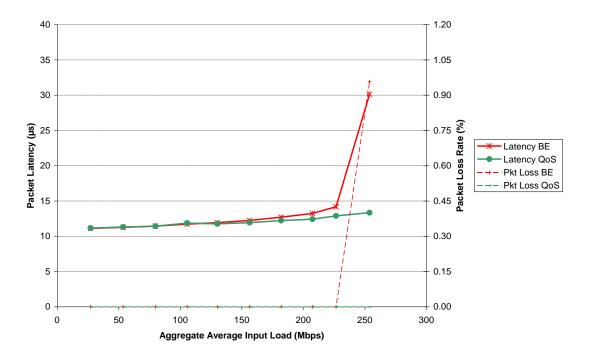

|    | 6.6.1.    | QoS-aware AutoRoute                                          | 202   |

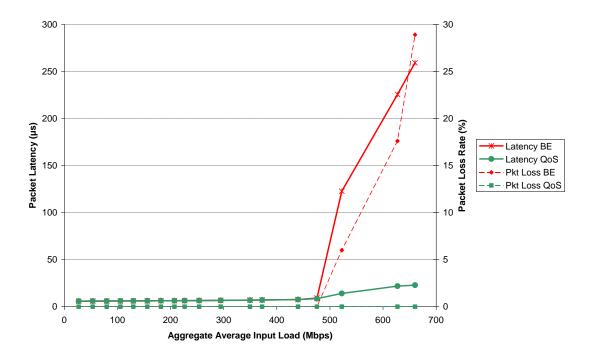

|    | 6.6.2.    | QoS-aware Packet Spraying                                    | 204   |

|    | 6.6.3.    | Spraying and HLU (S&H)                                       | 206   |

|    | 6.7. Cor  | nclusions                                                    | 209   |

| 7. | Conclusi  | on                                                           | 211   |

| •  |           | ntributions of this Thesis                                   |       |

| 7.2.    | Outlook to Further Work                                               | 215 |

|---------|-----------------------------------------------------------------------|-----|

| Appendi | x                                                                     | 219 |

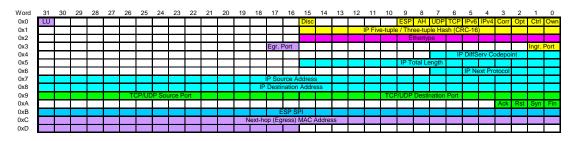

| Imple   | mentation Details of selected FlexPath NP-specific Functional Modules | 221 |

| Pre     | -Processor                                                            | 221 |

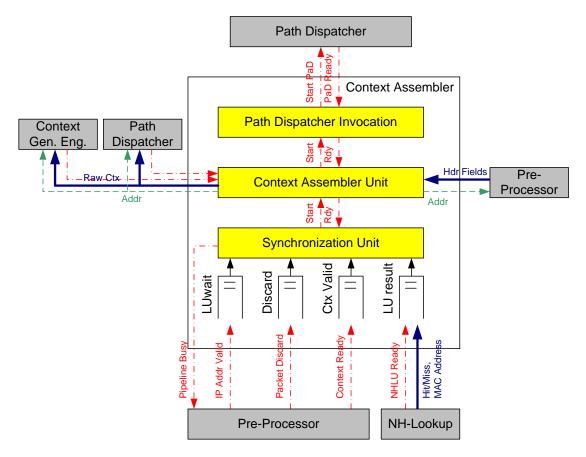

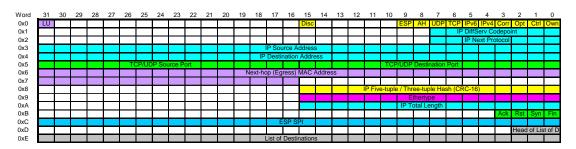

| Cor     | ntext Assembler                                                       | 223 |

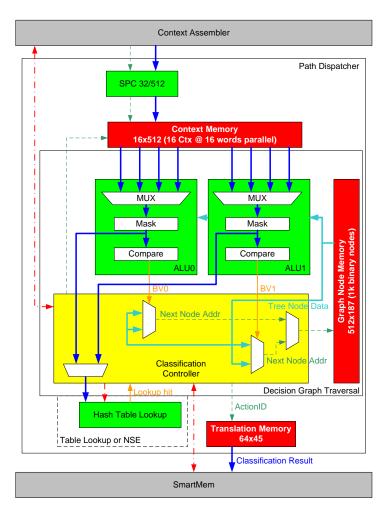

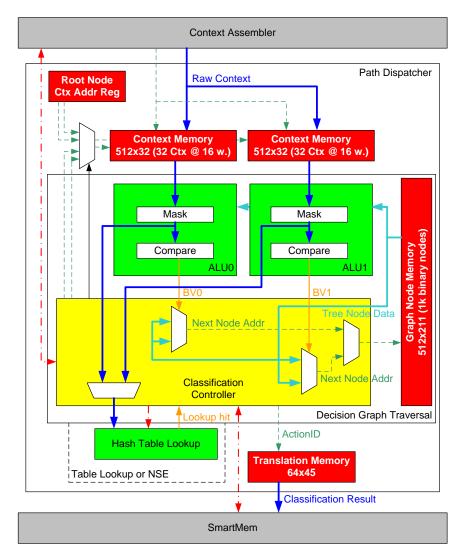

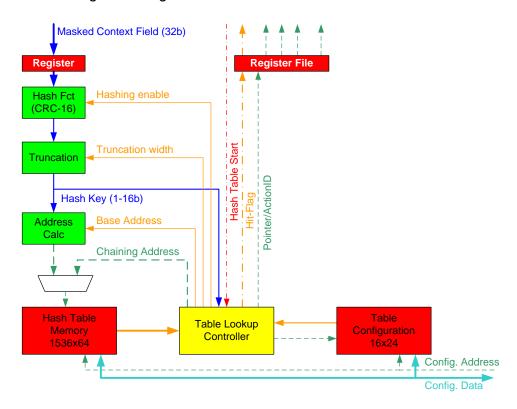

| Pat     | h Dispatcher                                                          | 225 |

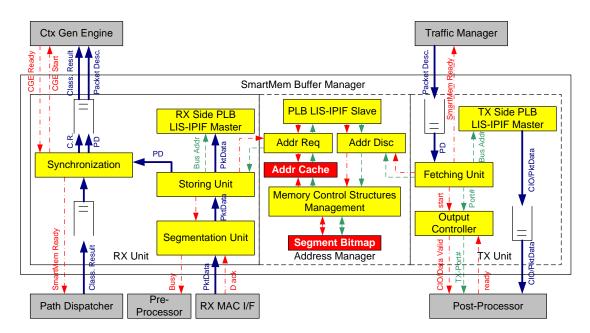

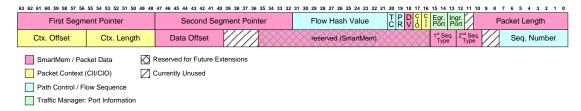

| Sm      | artMem                                                                | 230 |

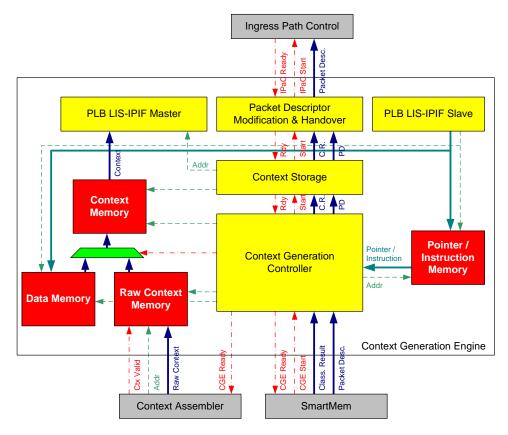

| Cor     | ntext Generation Engine                                               | 232 |

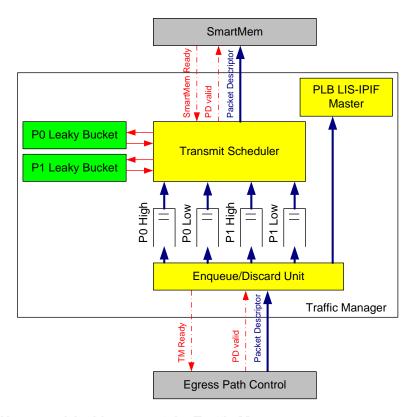

| Tra     | ffic Manager                                                          | 235 |

| Refere  | ences                                                                 | 237 |

| List of | f Figures                                                             | 249 |

| List of | Tables                                                                | 252 |

| Code    | Listings                                                              | 253 |

| Abbre   | viations                                                              | 255 |

| List of | f Prior-Printed Publications                                          | 261 |

## **Summary of the Thesis**

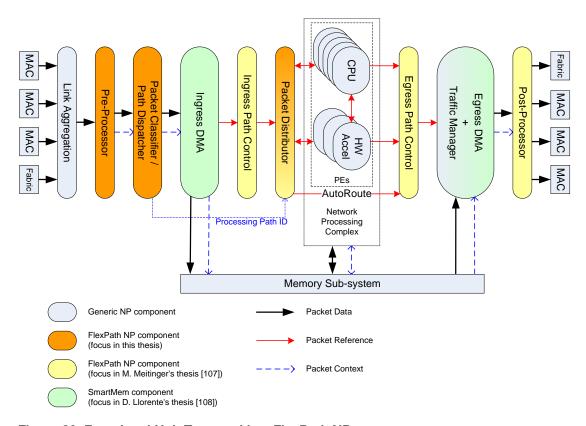

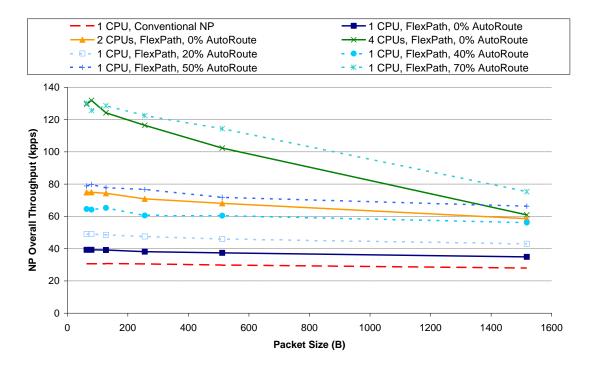

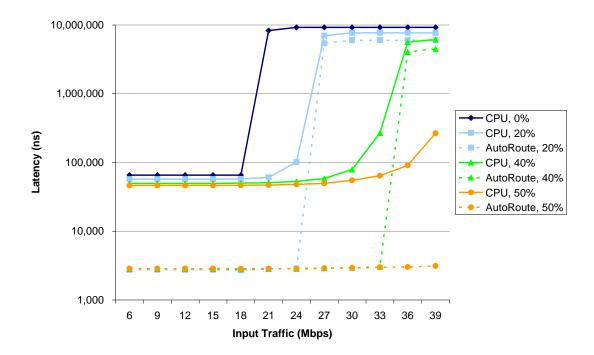

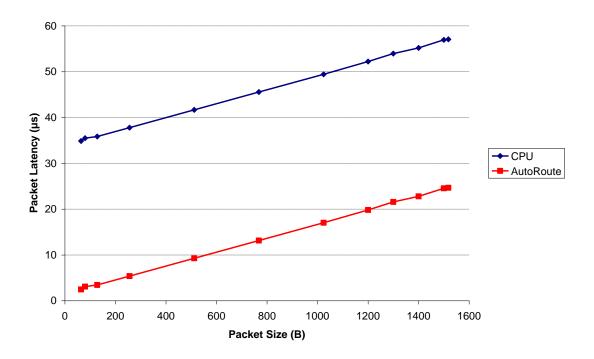

This thesis deals with improvements of switching nodes in Internet-based communication networks. During the past decade, increasing requirements for the networking infrastructure (i.e. routers, gateways, etc.) have led to the development of network processors (NPs). Network processors are highly integrated silicon components that achieve both high flexibility and performance. Contemporary networking infrastructure has to provide the flexibility of adapting to ever-changing new application needs, while the link speeds have increased to tens of gigabits per second with 100 Gbit/s already on the horizon. The current thesis proposes a new architectural approach to the network processing problem, in which dedicated hardware modules in the ingress and egress data path relieve a central processor cluster. The flexibility of the programmable processor cluster can be retained for those tasks that require this flexibility. More standardized tasks are solved by application-specific high performance hardware. Especially, a hardware unit for packet classification is proposed, which identifies the incoming traffic in real-time and dispatches the packets to the most suitable processing elements within the heterogeneous multi-processor cluster. Beyond a static processing path selection based on networking application characteristics, I have also investigated load balancing strategies that distribute the packets to paths supporting different qualityof-service levels within the NP. The presented hardware offload doubles the forwarding throughput of the NP in comparison to state of the art architectures with the same amount of processing resources.

# Zusammenfassung der Arbeit

Die vorliegende Arbeit beschäftigt sich mit Verbesserungen von Netzknoten in Internet-basierten Kommunikationsnetzen. Steigende Anforderungen an Netzwerkinfrastruktur (z.B. in Routern, Gateways, etc.) haben im letzten Jahrzehnt die Entwicklung von Netzwerkprozessoren (NPs) befördert. Netzwerkprozessoren sind hochintegrierte Siliziumbausteine, die gleichzeitig hohe Anforderungen an Flexibilität und Performance erfüllen. Die heutige Netzwerk-Infrastruktur muss flexibel genug sein, um sich an immer neu entstehende Anwendungsanforderungen anzupassen, während die Geschwindigkeiten auf den Übertragungsstrecken mittlerweile bei mehreren zig Gigabit pro Sekunde liegt und erste 100 Gbit/s Strecken in naher Zukunft folgen werden. Die vorliegende Arbeit schlägt einen neuartigen architekturalen Ansatz im Design von Netzwerkprozessoren vor, in dem dedizierte Hardware-Module im Ein- und Ausgangsdatenpfad den zentralen Netzwerkprozessorkomplex entlasten. Die Flexibilität der programmierbaren Ressourcen wird nur noch für die Aufgaben verwendet, die diese Flexibilität auch benötigen, während andere, besser standardisierte Aufgaben von spezialisierten Hardware-Modulen bearbeitet werden. Im Speziellen wird eine Hardware-Klassifikationseinheit vorgeschlagen, die den ankommenden Verkehrsfluss in Realzeit untersucht und die Pakete auf die für sie am Besten geeigneten Verarbeitungseinheiten innerhalb des heterogenen Multiprozessorclusters verteilt. Neben der statischen Verarbeitsungspfadwahl aufgrund Applikationsanforderungen, habe ich in dieser Arbeit Lastbalancierungsstrategien untersucht. welche die Pakete auf Pfade mit unterschiedlichen Dienstgütemerkmalen (quality-of-service) innerhalb des NP-Systems verteilt. Die vorgestellte Entlastung des Prozessorclusters ermöglicht eine Verdoppelung des Paketdurchsatzes im Vergleich zu einem herkömmlichen NP mit gleich vielen Rechenressourcen.

#### 1. Introduction

The work covered in this thesis is positioned in the context of Internet-based communication systems. I have proposed and investigated a new architecture for network processors (FlexPath NP) that optimizes the packet processing performance by providing different run-time reconfigurable processing paths and hardware-offload features that relieve the programmable processor resources. The following sections introduce the reader to the topic by describing the evolution of the Internet and give a high-level description of the packet processing infrastructure and networking application requirements. Based on these high-level observations, the fundamental ideas of the FlexPath NP architecture are mentioned and the introduction is concluded with the organization of the subsequent chapters of the dissertation.

Classical computer networks found in enterprises and universities, as home and office networks in residential areas and the server clusters operated by Internet service and content providers made up the Internet during the 1990s. Around the year 2000, an integration of the classical telephony networks (public switched telephone network, PSTN) and data networks took place. The introduction of Voice-over-IP (VoIP) protocols allowed transferring voice connections over asynchronous packet switched networks that were originally developed for data communication. Otherwise, backbones in the data networks started using Sonet/SDH technology with their high transmission bandwidth, which was originally developed to transmit high-order multiplexed voice signals in a strictly synchronous network. Around the same time, data services began to be offered by the mobile telephone providers (e.g. with GSM/GPRS and evolution towards 3G technologies found in UMTS), linking their networks into a unified, globally meshed communication network supporting both voice and data transmission.

The more widespread availability of the Internet to the general public and the increasing access speeds offered as customers were able to migrate from dialup connections (14 - 56 kbit/s) to DSL and cable modems (1 - 30 Mbit/s) also led to the introduction of new services, most importantly e-Commerce and multimedia. Those new applications, in addition to "plain" web traffic like http and email, required widespread use of cryptography for confidential data and a differentiation and prioritization of real-time from non-real time user applications. In a subsequent step, peer-to-peer applications, where individual users share content among each other (in contrast to the classical client-server model, where content is kept in a centralized place) caused an additional shift in communication patterns and increased the total traffic amounts in the Internet.

As a result of the above mentioned trends and developments, an exponential growth in Internet backbone transmission bandwidth with annual growth rates between

60% and 100% on average could be observed throughout the last decade [1]. This growth imposes significant pressure to improve the performance of the network architecture.

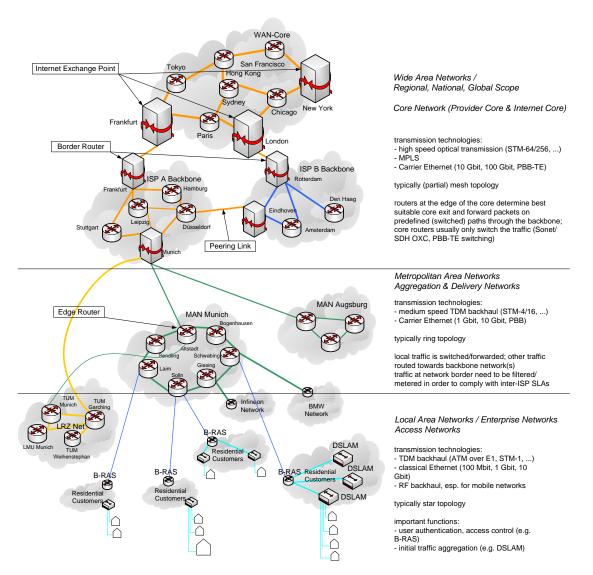

The networks making up the Internet are organized in a hierarchical fashion (see also Figure 1) with routers aggregating the traffic to and from smaller sub-networks and forwarding them towards the destination networks via peering or backbone links in the WAN core. Please note that the figure shows only the basic structure of the network aggregation and interconnection structure, the physical instances are not corresponding to an actual architecture, as such information is not publicly available from the actual ISPs.

Figure 1: Hierarchical Structure of the Internet

Residential customers and companies/universities connect to the Internet through the ISPs' points-of-presence, usually entering an aggregation network that combines the traffic originating from the same geographical region. Of course, these networks allow switching traffic directly between locally close neighbors, while networks lying further apart (this notion of distance applies also to networks attached to a different ISP operating in the same geographical region!) have to be reached through the wide area network. Although there exist some peering links between individual ISPs on a more regional level, the global connectivity is generally achieved through Internet Exchange Points [4], where so-called Tier 1 ISPs cross-connect their locally attached networks with each other.

Special gateway routers are found at the borders of the individual networks, so that the different providers have the ability to perform traffic monitoring and policing, and are able to translate traffic to a different protocol stack, which may be used in the adjacent network. The enforcement of inter-provider service level agreements (SLAs) at the network borders and eventual protocol conversions require a flexible router infrastructure with lots of general-purpose computing power. The same also holds true for the access equipment, where traffic first enters a provider's network and has to be inspected in order to achieve billing and accounting purposes as well as filtering functions, in order to block malicious behavior (B-RAS devices in Figure 1).

Traffic inside a provider's own network, which has to be forwarded between several internal switches or routers to reach the final endpoint of the network, is typically only forwarded without further packet inspection. In the Internet core, this is often achieved by using MPLS (multi-protocol label switching), which assigns preconfigured, locally unique labels for each of the predefined connections based on the initial routing information; and routers within the MPLS network perform a simple switching only on the MPLS labels rather than performing the traditional switching or routing function. As the MPLS labels are determined at the edges of an MPLS network by inspecting the IP destination addresses and QoS (quality of service) parameters of the packet, this kind of forwarding is often referred to as layer 2.5 forwarding [5]. In recent years, development of "carrier-grade" Ethernet technologies has started a trend among ISPs to simply switch the traffic based on L2 information rather than performing L3 routing based on the IP addresses in the packet.

As defined in RFC 1812 [2], routers are those functional entities in the network that perform the forwarding function with the help of routing protocols. As the variety of application layer protocols has increased dramatically since the early days of the Internet, and those applications come with greatly differing QoS requirements, DiffServ [3] has been introduced as a framework for differentiating traffic in the routers into different service classes and treating them in various different ways. Some of the necessary functions required to achieve QoS are packet filtering, metering and policing, and forwarding packets on different priority levels. Such QoS architectures are not only constrained to the IP protocol suite, but can also be found in recent Ethernet standards (e.g. VLAN IEEE 802.1Q), ATM and MPLS networks. In all places, where formerly unrelated networks are coupled together, gateways assure interoperability of the communication on both sides. In contrast to classical

routing, which is constrained to layer 3 of the OSI protocol stack, gateways may also work on higher layers up to the application layer (L7).

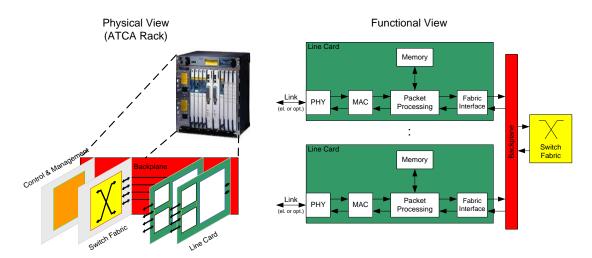

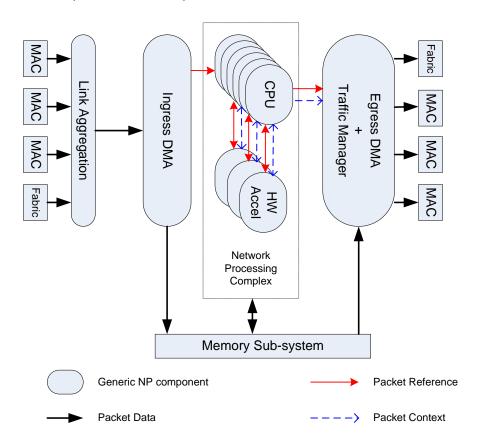

Figure 2 shows the modular architecture for routers and application gateways following standards such as AdvancedTCA [6]. The AdvancedTCA specification only provides standardization for the mechanical and electrical characteristics for rack-based communication systems (e.g. size of pluggable cards, electrical power supply, thermal power dissipation and a common backplane wiring scheme). Each vendor has the freedom to choose from a range of different backplane protocols and speeds and switch fabric parameters like line card connectivity and redundancy depending on the application requirements.

Figure 2: Typical Router Implementation with ATCA Standard

The actual packet processing takes place in one or several packet processing circuits on the individual line cards, while both line cards or the processing entities may be implemented in a half duplex or full duplex operation mode.

Traditionally, there existed high-performance ASIC (application-specific integrated circuit) solutions for high-speed switching in the telephony backbones. These solutions yielded a high performance, but as a hardwired function, they provided no flexibility / adaptability to newly emerging protocols and applications. A change in any of the transmission protocols comes at the cost of designing a new ASIC that can then be deployed in an improved line card. On the other hand, first routers in data networks were comprised of general-purpose PC systems with several network interface cards that implemented the forwarding functions and routing protocols in software. New protocols and functions could be easily deployed and tested by modifying the software, of course at a significantly lower performance level compared to the highly-optimized ASIC solutions.

With the integration of formerly separated networks and the advent of new applications and protocols around the year 2000, packet processing had to become

significantly faster while retaining the flexibility associated with the previous software implementations. Thus a migration of router technology from a general-purpose PC system to a custom-made ASIC (as they had been used in the telephony networks) would not serve the purpose. To address this performance / flexibility dilemma, network processors (NPs) were proposed to bridge the gap between slow but flexible general-purpose processors and high-performance ASIC implementations with their lack of flexibility and high development costs.

In general, NPs rely on a combination of application-specific instruction set processors (ASIP) and hardware accelerators. Hardware acceleration is used for networking-specific tasks that are common across many applications or where it is mandated by the computational complexity (e.g. cryptography). In addition, many NP architectures implement line / MAC / switch fabric interfaces on-chip and contain a set of memory controllers and connections to dedicated, off-chip hardware accelerators via standardized interfaces. This integration simplifies the board design of the router linecards and improves the overall system reliability, which is also an important aspect in the telecommunication industry. However, it is important to realize that no standard architecture has been found yet. Every NP vendor offers its specific solution, and designs from different suppliers look quite differently for NPs targeting different market segments and networking applications.

Based on an analysis of the first generation of network processors, the FlexPath NP architecture is proposed [7] that improves the performance of the NP by

- enhancing the software-programmable capabilities of the NP with hardware offload in order to relieve the processors from simple, recurring tasks faced across many networking applications and

- providing a variety of run-time reconfigurable processing paths (i.e. functional unit traversal sequences) in the data plane of the device that are optimized for the requirements of different networking applications.

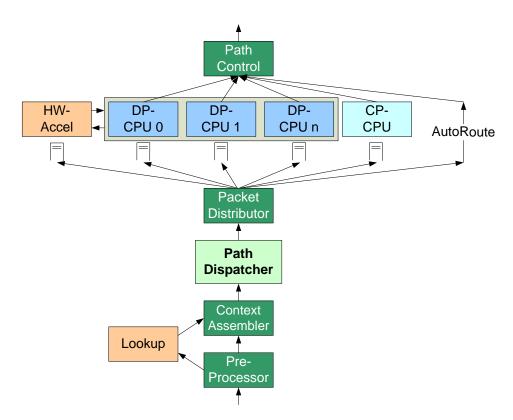

The fundamental idea behind the FlexPath NP architecture is to dynamically adapt the processing paths for the arriving packets so that the requirements of the current traffic load can be best met by the available resources in the device. A special hardware unit called Path Dispatcher performs a real-time classification of the incoming traffic into a set of application classes, for which optimized processing paths are provisioned in the FlexPath NP architecture. These processing paths include traditional programmable processor resources, arbitrary combinations of hardware offload units and software processors and a dedicated hardware-only forwarding path ("AutoRoute") for simple switching / forwarding functions. The classification function can be achieved by the heterogeneous decision graph algorithm (HDGA), which is fine-tuned to the constraints of on-chip real-time packet

classification at multi-Gigabit/s packet rates. In contrast to most state-of-the-art classification techniques, which operate on five or less different header fields, HDGA scales for rules bases with up to 20 dimensions. The architectural support for assigning the packets to different processing paths can inherently be used to address the load balancing problem among several parallel processing instances. This thesis presents a combination of packet spraying and hash-based load balancing (S&H) as a novel load balancing strategy, which achieves a high processor utilization and system throughput by taking into account the different characteristics and requirements of various networking applications.

The remainder of the dissertation is organized in the following way:

- Chapter 2 covers the complete state-of-the-art relevant to the individual contributions of this thesis, starting with existing commercial network processors and academic approaches in the NP field (section 2.1). The NP state-of-the-art is complemented by a survey of currently important and evolving networking protocols (section 2.2). Section 2.3 summarizes previous work in the field of packet classification techniques as a base for the derivation of HDGA. Finally, existing load balancing strategies for NPs are presented in section 2.4.

- Chapter 3 presents the FlexPath NP concept with its specific architectural modules based on an analysis of existing networking applications and NP architectures. The claims made during the presentation of the architectural concept are further supported by system-level performance simulation results, which focus on the potential of performance improvements that the hardware-offload aspects in a FlexPath NP offer compared to a traditional processor-centric NP architecture.

- Chapter 4 focuses on the Path Dispatcher unit, which performs the real-time packet classification task in the FlexPath NP system. The elaboration comprises the concept of HDGA, functional simulation results and finding an optimized architecture for efficient hardware implementation. The chapter is concluded with synthesis results for the Path Dispatcher unit in an FPGA demonstrator platform.

- Chapter 5 introduces a combination of two different load balancing schemes (packet spraying and hash lookup, S&H) that exploit optimum performance of the processor resources in a given FlexPath NP architecture. Functional simulation results are provided that compare the individual components and the combined scheme to several techniques of the prior art. The achievable performance benefits are shown based on realistic Internet backbone traffic traces.

- Chapter 6 presents the implemented components and system setup of a combined FlexPath NP / SmartMem demonstrator on a Xilinx Virtex-4 FPGA development board. Selected measurement results are presented that illustrate

#### Chapter 1 - Introduction

the performance of the FlexPath NP approach and prove the validity of the assumptions made during the concept development and simulations.

Finally, chapter 7 summarizes the scientific contributions of this dissertation to the state of the art and presents an outlook to possible future research directions based on the lessons learned during the FlexPath NP project.

The work presented in this dissertation originates from the FlexPath NP project, which was associated with the German research foundation's priority program "Reconfigurable Computing" (SPP 1148) during the time frame 2005 - 2009. Two dissertations cover the entire work performed in the FlexPath project, with the current thesis focusing mainly on the ingress data path pipeline elements and load balancing strategies and the other dissertation by Michael Meitinger ([107]) discussing the egress data path pipeline elements. For the demonstration purposes in both theses, we implemented a common demonstrator of a FlexPath NP on an FPGA development platform that also includes the SmartMem DMA engine, which was developed in a parallel project by our colleague Daniel Llorente, and is covered in his dissertation ([108]).

#### 2. State of the Art

The following chapter illustrates the state of the art for the work covered in this thesis, and is divided into three main topics:

- The first topic (section 2.1) focuses on the evolution of network processors during the past ten years and presents current implementation solutions and related academic approaches. In addition, the current application mix in the Internet is characterized (section 2.2) from which conclusions about the requirements for future networking compute architectures are drawn. The analysis of these two fields triggered the proposal of the FlexPath NP architecture, which is derived in detail in chapter 3.

- The second topic (section 2.3) focuses on existing approaches in packet classification. This field is relevant to the major contribution of this Dissertation, the HDGA packet classification scheme implemented in the Path Dispatcher, which is presented in chapter 4.

- The state of the art survey is concluded by discussing approaches to load balancing in network processors (section 2.4), which is an important function in multi-processor systems in general. Load balancing in the context of FlexPath NP is addressed in chapter 5.

#### 2.1. Network Processors

#### 2.1.1. Commercial Network Processor Architectures

#### 2.1.1.1. Commercial NPs Prior to the FlexPath NP Proposal

Although the survey on NPs undertaken by Shah [9] dates back to the year 2001, this document provides an excellent starting point for understanding the evolution of the network processor field. Therefore, a selection of NPs from that period should be presented first in order to show the evolution of these devices and draw conclusions about the architectural trends that have taken place in the market ever since.

The Agere Payload Plus NP [10] is a multi-chip solution that consists of a Fast Pattern Processor (FPP) and Routing Switch Processor (RSP) in the data path and the Agere System Interface (ASI) for control plane functions and communications with a management host. The FPP receives the packets from the link, parses the packet and hands it over to the RSP chip. The FPP consists of a multi-threaded, pipelined processor and hardware assists for pattern matching and checksum / CRC calculations. The RSP chip receives the packets from the FPP along with certain classification information and performs traffic management, traffic shaping and queuing functions before performing final modifications on the packet and sending them out towards the switch fabric. The functions are implemented with three dedicated VLIW (very long instruction word) processors: traffic management compute engine, traffic shaper compute engine and stream editor compute engine. In addition to the VLIW processors, the chip provides interfaces to external SDRAM to store the packets while they are being queued.

The MSP5000 processor from Brecis Communications [11] addresses converged voice and data communications linking enterprise sites to the network edge. The task is achieved by two DSP (digital signal processor) processors for voice and packet processing while a MIPS RISC (reduced instruction set computer) core takes over control plane functions. The processors communicate with a special QoS-aware system interconnect (Multi-Service Bus Architecture) with a peak data rate of 3.2 Gbit/s. The processors are complemented on-chip with a set of hardware accelerators for cryptographic functions and CRC (cyclic redundancy check) calculation.

IBM's Power NP [12] is a representative of a massively parallel processor cluster. Apart from a single general-purpose PowerPC that is used for control plane processing, it features an embedded processor complex with 16 programmable protocol processors. In addition to the 16 cores, there are seven specialized hardware accelerators for DMA (direct memory access), checksum calculation, traffic shaping and policing and inter-processor communication.

The PXF NP from Cisco [13] features 16 processors arranged in eight parallel pipelines. The pipeline depth may be extended by chaining several PXF chips in a router system. By forcing the packet processing task into a pipeline structure, with every processor performing only a specific sub-task, a deterministic behavior of the NP with respect to packet throughput may be achieved.

Intel's IXP 1200 NP [14] also follows the processor cluster architecture found in the IBM Power NP. It provides six multi-threaded microengines that support a total of 24 tasks in the system. The instruction set of the microengines is specifically optimized for packet processing and they have to be programmed in their own assembly language in order to achieve maximum performance. The NP comes with integrated hardware support for hashing and queue management and features a StrongARM RISC processor for control and management purposes.

The X40 NP from Xelerated [15] targets the high speed end of the NP spectrum. It consists of a single pipeline with 10 stages; each stage consists of a classification and action stage. The action stage is made up of a packet instruction set computer (PISC), which is a processor with a specialized ISA (instruction set architecture) for packet processing. In addition, the chip allows accessing external memory and CAM (content addressable memory) from all pipeline stages. During operation, every stage in the pipeline works on a different packet and completes processing within a single clock cycle, thus achieving very high packet rates.

#### 2.1.1.2. Evolution of the Commercial NP Field after the FlexPath NP Proposal

Following the burst of the New Economy bubble, a wave of consolidation started in the NP business. Some vendors went out of business, others were acquired by larger companies or product lines were spun off to new companies. Successful product lines, e.g. Intel's IXP product line, evolved over several generations. More processor cores were added to the system, interconnect structures upgraded, memory and I/O interfaces adapted for newer standards [16] and the devices were scaled down to new CMOS process generations. Starting with the IXP2400 series of NPs, the microengines were equipped with special "next-neighbor" interconnect registers. They allow very efficient passing of data among neighboring microengines, thus enabling a pipelined programming model in addition to the parallel processor cluster model of the IXP1200 series. Moreover, a further differentiation for the various targeted market segments could be observed. In 2005, processors from the second generation existed in a range of two to 16 microengines, clock frequencies between 600 MHz and 1.5 GHz and target line rates between 1 Gbit/s and 10 Gbit/s. The latest model (IXP2855, [17]) also features two hardware crypto cores that enable IPsec processing at up to 10 Gbit/s. However, in 2007 Intel sold its NP line to Netronome, which will further develop NP products evolving from the IXP28xx.

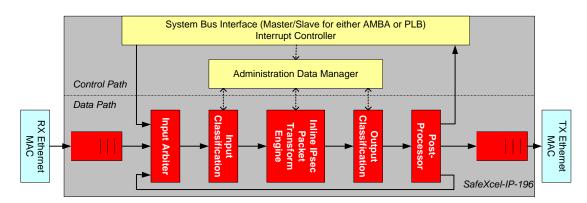

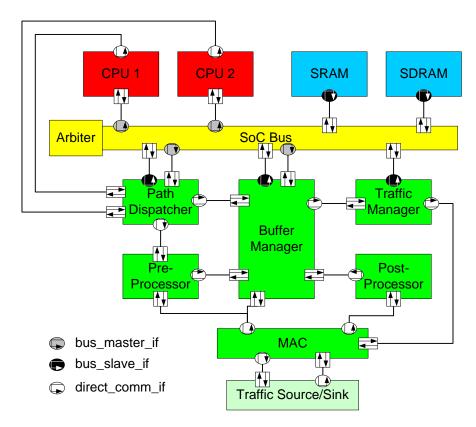

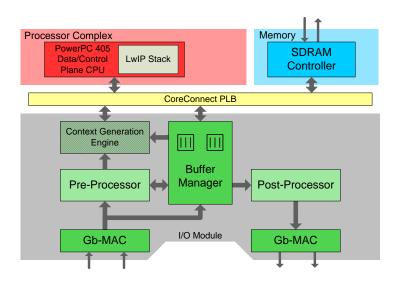

In January 2006, SafeNet announced the SafeXcel IP inline security engine [18] as a security application co-processor that works as a full-fledged offload for security application handling from general-purpose compute architectures in network processor SoC designs. The security engine can be used either as a traditional co-processor, relieving the general-purpose parts of the NP from the compute-intensive cryptographic algorithms, but it can also be integrated as an autonomously operating processor in "bump in the stack" (i.e. packets are en-/decrypted before reaching the processor, so that the processor sees only plaintext packets) or "bump in the wire" (i.e. packets are processed without even being touched by the processor) use cases. Especially the last mentioned "bump in the wire" use case is based on essentially the same idea as the proposed AutoRoute feature in a FlexPath NP, which will be described in detail in chapter 3.2. The architecture appears to be commercially successful, as the device is still actively marketed in 2009 [19]. Figure 3 shows the architecture of the SafeXcel-IP-196 block as of 2009.

Figure 3: SafeXcel-IP-196 IP Flow-Through Packet Engine

The nP7300 from AMCC [20] follows the run-to-completion operation model (Figure 4a) with three nPcore processors, each of which supports 24 tasks. From the point of view of the NP programmer, the system performs like a 72 core processor, while the packet processing task for each packet is executed in a single thread. Consequently, there is no multi-processor overhead necessary during software development, i.e. the programmer does not need to consider splitting the application into several chunks, which might be distributed among the processors and organize data communication and synchronization between the cores. The data plane processor complex is enhanced with a Channel Service Module (CSM) that provides an autonomous DMA function to store and retrieve packets from the I/O interfaces without processor intervention. The chip also includes a dedicated traffic manager for traffic shaping, policing and queuing and a separate hashing unit. Memory and external co-processors (e.g. TCAM memories) can be accessed via standardized interfaces. The nP7300 has no dedicated control plane processor on chip, but can be connected to a host via 10/100/1000 Ethernet and the data plane is targeted for 10 Gbit/s half-duplex operation.

Netronome's NFP3200 NP [21], which is the first successor of Intel's IXP28xx product line, now features up to 40 microengines for data plane processing with local instruction stores optimized for run-to-completion or pool-of-threads programming models. In addition, an ARM11 embedded RISC core is used for IPsec key exchange algorithms, routing table updates and system management functions. The NP also comes with a hardware cryptography module that supports up to 10 Gbps, while the 40 microengines allow packet processing at 30 Mpps or 20 Gbps with 2,000 instructions per packet.

In 2008 Cisco released information about its own Quantum Flow Processor [24], which is initially a two-chip solution with one chip for the processors and a second chip for traffic management. The processing chip consists of 40 Tensilica RISC processor cores [25] that are C-language programmable and provide four threads per core at 900 MHz to 1.2 GHz. The packets arriving from either the line interfaces or the switching fabric are first handled by the traffic manager chip, which also provides access to a centralized memory and includes all system I/O interfaces. When the packets are ready for processing, they are dispatched to one of the 160 threads in the processor engine chip, which are connected with the rest of the system via a crossbar switch architecture. The initial two chip solution will be used in Cisco's ASR 1000 series aggregation switch routers with an internal packet processing capability of 5 to 100 Gbps. There are plans to integrate the system into a single chip design and increase the number of processor cores in the packet processor engine in future versions of the NP.

Another current design that adheres to the parallel processor cluster architecture is the Octeon II processor family from Cavium Networks [26], of which first processors are announced to ship in the fourth quarter of 2009. The NP family will feature a new generation of 64bit MIPS cores in the data plane. There will be devices with 1 to 32 cores, each of them running between 800 MHz and 1.5 GHz. There are also up to 75 hardware accelerators available in the system, which are connected to the cores via an eight Tbps Hyperconnect crossbar switch. The first NP generation targets the 40 Gbps market but is claimed to provide I/O capabilities for up to 100 Gbps.

Xelerated still pursues the strict pipeline approach (Figure 4b in section 2.1.3) with its X11 NP [22] released in 2008. In contrast to the X40 [15], the X11 features five blocks of 32 pipelined PISC processors, thus 160 processors in total. External memories and hardware accelerators may be accessed only from distinct Engine Access Points (EAP) at the beginning of each of the five pipeline blocks. The EAP includes packet buffers to cope with the latency associated with the individual accelerators or memory accesses. With a core frequency of 240 MHz the X11 is able to process packets at up to 24 Gbps. Xelerated has also announced a new generation of network processors (HX family) that addresses the evolving 100 Gbps Ethernet market. In comparison to the X11 NPs, the number of processors in the

programmable pipeline is increased to 512 and the devices feature an integrated traffic manager and switch fabric [23]. It is characterized by Xelerated with the term "linecard on a chip", due to its high level of integration that needs only external DRAM, TCAM (NSE) and PHYs as additional off-chip elements.

#### 2.1.2. Academic Network Processor Projects

#### 2.1.2.1. Academic NP Investigations Prior to the FlexPath NP Proposal

The Field-Programmable Port Extender (FPX) developed at Washington University in St. Louis [27] in 2001, provides an FPGA-based reconfigurable platform for network processing for ATM. The platform comprises an extension board with two FPGAs, which can be plugged in between the line card and switching backplane interfaces of an ATM-based Gigabit switch (WUGS). The first FPGA, which comprises a simple, reconfigurable switching fabric with a small control memory allows to route incoming traffic on a flow-level granularity (i.e. ATM VPI/VCI numbers) between the line card interfaces, switching backplane and two dynamically reconfigurable slots in the second FPGA. In addition, by sending special control cells to this FPGA, bitstreams for the second FPGA can be transmitted over the network, allowing a subsequent (partial) reconfiguration of the other FPGA. The second FPGA contains two reconfigurable slots for the actual user-defined packet processing functions and has interfaces to external SRAM and SDRAM. The FPX platform has been used to demonstrate IP packet routing, per-flow queuing and flow control and applicationlevel content inspection and modification. By making use of reconfigurable FPGA resources in the network processing device, the benefits of run-time modification of the packet processing function can be combined with the hardware-like performance of the FPGA logic.

In 2002, Troxel et.al. from the University of Florida at Gainesville [28] propose a network processor architecture that allows to dynamically reconfigure the pipeline depth of microengines in an Intel IXP1200-like processor configuration during system runtime in order to improve the overall system performance given fluctuations in the arriving traffic pattern. The authors present only simulation results of the proposed system. Assuming that the networking application can be executed on microengine pipelines of various depths (i.e. the task can be partitioned to run on one, two or three engines with different resulting processing times per processor), they can exploit a performance gain by changing the pipeline depths assigned to different traffic types during the system runtime. They present an application scenario from a defense application with three different packet types, so that a generalization to Internet traffic is not straightforward.

The PRO3 network processor proposed by Papaefstathiou et.al. from Ellemedia and the Technical University of Crete [29] in 2004 introduces dedicated hardware support for DMA and queuing operations in the NP SoC and enhances two

programmable RISC cores with two dedicated hardware accelerators. The field extraction unit (FEX), which is a firmware-configurable hardware assist, parses the incoming packet and may write important header fields into the register file of the processor. The processor can then execute the actual high-level part of the networking application and the field modification unit (FMO) is available for writing back results from the RISC core registers into the packet, which may include bit-and byte-level operations that are hard to implement efficiently in the general-purpose RISC core. The authors show, that a PRO3 system with two FEX-RISC-FMO pipelines achieves a similar performance for benchmark TCP and UDP applications in comparison to the Intel IXP2400 with 6 microengines. In addition, they could demonstrate that the hardware-based queue management in the PRO3 is significantly more efficient than the standard software-based solution in the IXP, such that both systems could deliver roughly the same performance, while the PRO3 chip consumes only about one fifth of the IXP's die area.

In 2005, Ravindran et.al. from the University of California at Berkeley [30] investigated the forwarding performance of a network processor architecture based on parallel Xilinx Microblaze processor pipelines. After optimizing the partitioning of the IPv4 forwarding application onto a three-stage pipeline, a total system throughput of 1.8 Gbps can be achieved with a total of 12 Microblaze processors in four parallel pipelines. This value is compared to the forwarding performance of an Intel IXP2800, which achieves 10 Gbps with its 16 optimized microengines. After normalizing the results to chip area, the authors show that the FPGA-based solution performs only a factor of 2.6 worse than the commercial NP. The claimed benefit of the FPGA solution is that by using soft processor IP with the provided toolchain and standard off-the shelf FPGA products is an attractive choice for niche application domains, where the cost of starting a full ASIC design may be too high in comparison to the expected number of units to sell.

#### 2.1.2.2. Academic NP Investigations after the FlexPath NP Proposal

DynaCORE ([31], chapter 16, pp. 335-354 and [90]), which was developed at the University of Lübeck in 2006, is a dynamically reconfigurable co-processor for compute-intensive payload manipulations in network processor systems. The FPGA-based architecture combines the near-hardware performance of an FPGA implementation with the dynamic partial reconfiguration capabilities offered by Xilinx FPGAs. The static part of the DynaCORE provides system I/O interfaces for communication with the off-chip NP (e.g. a commercial NP or our FlexPath NP demonstrator system (see [91])) and a controller for system monitoring and reconfiguration management. As requests arrive from the attached NP to execute cryptographic algorithms or pattern matching applications on the arriving packets, the reconfiguration controller insures that a sufficient amount of hardware accelerators is dynamically configured into the reconfigurable slices of the system

and forwards the incoming packets to the respective unit. Correct routing of the packets and glitch-free operation of the DynaCORE during partial reconfigurations is achieved by a special network-on-chip architecture called CoNoChi.

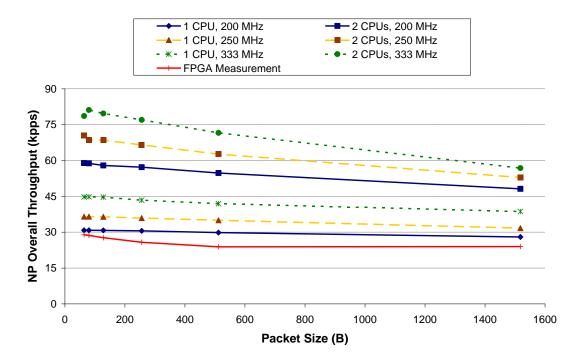

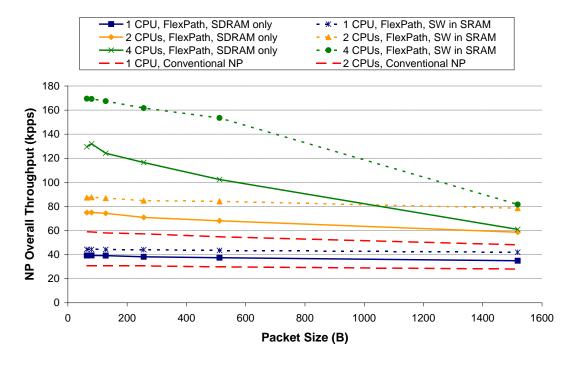

Another run-time reconfigurable NP architecture was presented by Kachris et.al. at the University of Delft in 2006 ([32]). They regard an NP architecture based on a Xilinx FPGA with either the Microblaze soft core or PowerPC hard core processors as central processing elements. These programmable resources may be assisted with hardware accelerators for Checksum calculations, DES encryption or IDCT transcoding as representative examples for plain IP forwarding, IPsec or voice/video application processing. The respective functionality may however also be achieved by the processors (at a lower performance level). Now, Kachris assumes different shares for the individual networking applications and computes an optimum combination of accelerators (type and quantity) in order to maximize throughput. During system runtime, the current load on the network interfaces is monitored and the hardware accelerators are dynamically reconfigured in order to yield maximum utilization of the available soft- and hardware instances.

The GigaNetIC architecture [33] developed by Niemann et.al. at the University of Paderborn in 2007 proposes a massively parallel multi-processor system for networking applications. Clusters consisting of four embedded RISC processors with local memories and hardware accelerators are interconnected using a 2D-mesh network-on-chip. Peripherals and hardware assists with system-wide relevance (e.g. Ethernet cores, IPsec accelerators, etc.) may be attached directly to the NoC and are thus universally reachable and can be accessed as a shared resource. In this way, the proposed architecture allows finding balanced solutions between locally The authors claim C-language shared globally shared resources. programmability for the embedded processors and an architecture that may be programmed either as a functional pipeline or as run-to-completion cluster. Benchmarking results are presented for a simple TCP/UDP integrity check and forwarding application. Results from an FPGA-prototype implementation with only two processor clusters (total of eight cores) and two NoC switches are also extrapolated for an ASIC implementation with 20 clusters (total of 80 cores). The ASIC implementation would consume the same die area as current state-of-the-art desktop processors. The GigaNetIC is shown to have a forwarding performance which is roughly one order of magnitude greater than that of the general-purpose CPU, but it consumes about two orders of magnitude less energy. However, the authors give no comparisons to commercial NP implementations.

In 2006, researchers from Hitachi present investigations on a cache-based network processor architecture ([34]). A conventional NP cluster with parallel/pipelined processors is augmented with a hardware pipeline that provides pre- and post-processing capabilities and the cache system. The first packet of each packet

stream/burst is forwarded to the processor cluster, where the traditional forwarding function is implemented in software. After processing, all relevant information (i.e. flow identification and all types of packet manipulations / data) are recorded in the cache system. When a subsequent packet of the same flow arrives, this information is retrieved from the cache and may be applied on the packet in the post-processing stage. Measurement results performed on an FPGA prototype with real world Internet traffic revealed, that between 10% and 40% of the total processor cluster performance is sufficient to forward 100% of incoming traffic. In turn, the authors argue that a traditional 10 Gbps to 40 Gbps NP device augmented with their cache implementation would be able to process a 100 Gbps link in a lossless fashion. Such an implementation would in turn only consume about 45% of the power needed in comparison to a conventional NP that is scaled up to 100 Gbps performance.

In 2007, Li et.al. from the National University of Defense Technology in China proposed the DynaNP architecture ([35]). A DynaNP consists of a set of processors that are connected over a central interconnect to shared memory and ingress / egress management engines (IME, EME), which perform a DMA function to and from the shared buffer and initial packet pre-classification. The networking application is partitioned into tasks, which are subsequently assigned to run on distinct processors. Depending on the type of arriving packet, processing may be achieved by executing a variable number of tasks. The initial packet classification in the IME determines the first task to be executed for the incoming packet and subsequently assigns it to the queue of the respective processor. After processing each task, the processor decides whether further steps are necessary (sending it on to another processor) or back to the EME for retransmission over the link or fabric interfaces. As an initial partitioning and mapping of the total task set among the available processors will not be optimally balanced, and the utilization of individual processors is also expected to change with variable traffic loads, the authors propose a dynamic task migration algorithm, with which they essentially perform load balancing of the tasks among the processor cluster. The publication presents system-level simulation results of the proposed DynaNP architecture. However, the elaboration lacks a prototypic implementation and the authors do not comment about the overhead associated with frequent task migrations and how to insure packet ordering when reconfiguring the processing paths.

#### 2.1.3. Conclusions

The characteristics of the first and second generation of NPs form the basis, from which the FlexPath NP architecture [7] was initially defined:

- A number of different companies have developed NPs for different market segments with quite different architectural approaches and processing resources.

- All regarded NPs combine programmable resources with hardware accelerators for compute-intensive and networking-specific tasks. Most NPs also include line and fabric interfaces and memory controllers for off-chip packet storage. Control Plane functions, which are not performance-critical are usually mapped to a general-purpose RISC processor. For the packet processing task, RISC processors, some of them with application specific instruction set extensions, DSPs, or traditional ASIP designs are used.

- While there are also some multi-chip solutions, most designs favor integration into a single chip design.

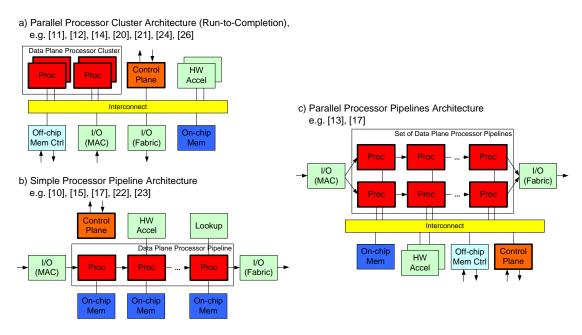

- Due to the performance requirements of network processing, multi-threading and parallel processing are widely used. Multi-threading allows hiding long memory or hardware accelerator access latencies, as the programmable core can continue working on other packets being processed in different threads. As far as operation models are concerned, processors may be used in a symmetric multi-processor cluster (run-to-completion architecture), a dedicated processor pipeline, or a combination of both (parallel pipelines). Figure 4 illustrates these three architectural approaches in an abstracted form.

Figure 4: Fundamental NP Architectures: run-to-completion parallel processor cluster (a), simple processor pipeline (b), and parallel processor pipelines (c)

More recent developments in the commercial NP field can later be used to analyze the industrial relevance of the proposals made in the FlexPath NP approach. The following conclusions about commercial network processor architectures may be drawn with respect to the subsequent features:

- Programmability: Programming network processors is still an important challenge for some devices. As far as the data plane processors consist of cores with packet processing specific instruction sets, no standard compiler tool chain may be available. Consequently, those cores have to be programmed in their own assembly language, which can become quite awkward. Big vendors, such as Intel have therefore provided software libraries that include optimized code for a big variety of commonly needed protocols. However, the possibility of simply and efficiently upgrading an NP-based system in the field with new software patches for new protocols is somewhat limited. In contrast, some vendors resort to standard embedded cores that are programmable in C, like Cisco's QFP or the MIPS core used in the Cavium Octeon II. As integration density has improved largely, it is now possible to trade off the comfort of C programming on a few more standard embedded RISC cores versus fewer processors featuring an application-optimized instruction set. Another programmability aspect can be found when comparing the run-to-completion solutions with the pipelined architectures. Pipelined architectures have the inherent advantage of a deterministic behavior, and thus a fixed maximum packet rate. The fixed packet rate is helpful when a manufacturer guarantees operation of his device for a given speed rate, as a worst case scenario with a continuous stream of shortest size packets leads to a fixed packet rate for any given line speed. On the other hand, this guarantee comes at the price of having to partition the application into chunks that can be executed within the individual pipeline stages in the mandated time. Also, when there are only limited access points to external accelerators and memories, this restricts the freedom of software programmable solutions.

- Interconnect: As NP manufacturers have scaled up the number of processor cores in run-to-completion architectures, traditional on-chip buses have become a system bottleneck. Therefore, a migration to more sophisticated structures such as crossbar switches were necessary in order to fully exploit the processing performance of the larger processor clusters. In contrast, pipelined architectures may be implemented easily, as they require only simple point-to-point connections between neighboring processing elements. In addition to the guaranteed throughput that pipelined architectures can offer, this explains, why NPs targeting the highest speed market segment still adhere to the pipeline model.

- Processors: Current packet processors are predominantly RISC processors, some of them with a customized instruction set. Other processor types such as

the MSP5000 from Brecis Communications [11] with DSPs or VLIW processors (Agere, [10]) are no longer found in current designs. Specific high-performance tasks are still solved by means of hardware support, and not mapped to software programmable units. However, there is a strong trend towards multi- and even manycore processors, and multi-threading is used extensively in order to hide accelerator and memory access latencies. As packet processing usually treats the packets as independent units, packet processing can be far easier parallelized than traditional general-purpose compute applications. The advances made in modern CMOS process technologies helped increase the clock frequencies of the processors from a few hundred MHz in the early NP designs to well above the GHz margin.

- Hardware Acceleration: For compute-intensive tasks in packet processing, such as CRC checksum calculations or IPsec cryptographic algorithms, only hardwired logic is able to deliver real-time performance for current link rates. But also other fixed and standard tasks such as queuing and DMA that have to be performed for every packet are often offloaded to dedicated hardware units. In total, one can observe that both the variety and number of instantiated accelerators has been increased in parallel with the number of processor cores and the cumulated line rates on current router blades.

- Integration: The shrinking process technologies not only allow scaling chips towards containing even more processor cores and dedicated hardware units. Integrating as much functions as possible into a single chip design also helps to significantly reduce design complexity and cost and it increases reliability. Complex and expensive interconnects across printed circuit boards can be saved, if it is possible to integrate the entire processing chain from the MAC interfaces and the actual processor complex towards the switch fabric interface and memory controllers into a single chip. These single chip NPs are currently standard, except for the most processing intensive solutions for the highest possible speed grades (e.g. Cisco's ASR 1000 router, which provides deep packet processing performance in the multi-Gigabit domain).

- Specialization: While initial NP design proposals tried to address the problem of network processing with a full breadth approach, recent developments show a strong differentiation of the devices that target individual market segments. Devices for high-speed switching and routing in backbone networks are typically addressed with high-performance pipelined processors and hardware support for lookups, CRC calculations and traffic management. The processor architecture can be optimized to efficiently execute the functions on Layers 2 to 3 of the OSI stack, and don't have to provide as much general purpose processing power as for application layer or deep packet processing. In contrast, the parallel processor architecture NPs are more ideally suited for edge and access network

deployments, where the individual line rates may be slower than in the aggregated network core, but access control, intrusion detection, QoS policing, etc. have to be performed on the incoming packets. These deep packet processing applications, which may work on the higher protocol layers or even parts of the packet payload in addition to the pure L2/L3 forwarding can be better achieved with a more general-purpose processor and a single-threaded, run-to-completion processing model. Traditional router deployments in central office environment are typically implemented using rack-mounted systems with the possibility of scaling the performance by adding additional line cards or switching fabrics as needed. In contrast, smaller form factors with the NP as SoC solution and only few peripherals on a single PCB are available for mobile network base stations or customer premises equipment. The employed NPs need less processing performance and come with less cores and lower operating frequency to provide more power efficient systems.

Regarding academic network processor concepts, ideas from the following research areas have been investigated by the research community:

- Reconfigurable computing: several projects ([27], [31], [32]) have used the reconfigurability of FPGA devices in order to adapt an NP during runtime to changing conditions in the incoming traffic. In addition, by making use of reconfiguration, the functions implemented in the device may be almost as easily changed as in a conventional software system, but the performance of FPGA hardware accelerators is more similar to that of ASICs.

- Hardware offload: The PRO3 project [29] demonstrated the benefits of assisting general-purpose processors with networking-specific configurable hardware. A more radical kind of offload is proposed by Hitachi [34], where a full packet forwarding path is implemented in hardware that is controlled by the contents of the packet processing cache.

- Interconnect: The GigaNetIC project [33] pointed out an architecture that is well suited for scaling to much larger numbers of programmable resources. As commercial manycore NP designs moved away from shared bus architectures towards crossbar switches and processor pipelines, the GigaNetIC proposes a network-on-chip (NoC) based design.

# 2.2. Networking Applications

## 2.2.1. IP Forwarding

The traditional task of routers is forwarding of IP packets towards their final destination. The associated tasks are defined in RFC 1812 [2] for IP version 4, which is still the dominant IP version today. After packet reception, the link layer information of the packet is discarded. Next, the router has to validate the IP header, which includes checking the IP checksum and the time-to-live field in the packet header. If the packet is valid, the IP destination address is used together with the routing table information to determine the output interface onto which the packet has to be forwarded. The CIDR addressing scheme [36], which is currently used for IPv4 mandates a longest prefix match of the destination address versus the prefixes stored in the routing table. Finally, the time-to-live field has to be decremented by at least one and the IP checksum must be re-calculated. After that a new link layer header may be appended to the packet and the packet can be placed into the output queue associated with the determined physical output port. In this best effort scenario, all IP packets are treated with equal priority, such that no QoS guarantees will be given by the network.

#### 2.2.2. QoS Mechanisms

With the introduction of multimedia applications over the Internet, the traditional best effort forwarding model of the Internet has proven to be insufficient. Two alternative architectures have been proposed to allow service differentiation in the Internet and give priority to certain packets over others.

In the IntServ model [37] proposed in 1994, hosts or routers can establish virtual connections with certain associated performance guarantees. If the routers along the connection have sufficient resources available, the virtual connection is accepted and packets of this connection are treated separately from the other traffic. This separation requires some kind of input filtering or access control and metering whether the traffic does not exceed the predefined service parameters such as a bandwidth limit. In addition, the router must provide different queues and a scheduling mechanism that insures proper multiplexing before the output interfaces. Due to the requirement of establishing virtual connections and having to classify each incoming packet against the full set of connections, this approach is not scalable to a large number of users and is therefore only rarely used.

In contrast, the DiffServ architecture [3] proposed in 1998 uses the old type-of-service field in the IP header as DiffServ codepoint (DSCP) to indicate that a packet belongs to a certain predefined traffic class. The network operator associates a certain per-hop-behavior with each DSCP, which may include parameters such as maximum allowable bandwidth, forwarding and queuing priority, etc. The individual

packets have to be marked with valid DSCP values either by the end hosts (if they know about the network operators' traffic classes), or by the border routers sitting at the edge of the DiffServ network. For the routers within the network there is the big advantage that no state information has to be maintained. The forwarding function is simply inspecting the DSCP field when determining the processing priorities or queuing priorities. Thus, a full classification and policing of the individual packets only happens once at the network edge. Within the DiffServ network the DSCP value determines the forwarding behavior, which is typically limited to around ten different classes [38]. Therefore DiffServ scales far better and may be easier implemented compared to IntServ. The concept of marking individual packets with short QoS identifiers has been considered successful enough, so that the same concept is now also implemented in the most recent carrier grade Ethernet standards (see chapter 2.2.6).

# 2.2.3. Security Applications

As the Internet evolved from a pure academic research network towards a ubiquitous communication network, transmission of sensitive information (like trade secrets, financial information, etc.) caused serious security and privacy concerns. In order to tackle these challenges, authentication and encryption technologies had to be provided. The IPsec framework [39], which became initially standardized along with IPv6 in 1998, provides those services for both IPv6 and IPv4. The IPsec framework consists of the two data plane protocols encapsulating security payload (ESP) and authentication header (AH).

The AH protocol only assures that a packet comes from the claimed sender, and that the packet did not get modified en route to the receiver. This is achieved by applying cryptographic operations on the header and by calculating a cryptographic checksum over the payload. However, the payload itself is not encrypted, and can therefore be read by anyone tapping into the communication path.

The ESP protocol encrypts the payload, i.e. the original content of the packet is no longer legible for others between the two IPsec endpoints. Standards-conforming implementations (current RFC from 2005) have to support AES and 3DES algorithms for encryption of the payloads and HMAC-SHA1 as cryptographic checksum.

IPsec implementations make use of two databases:

- Security Policy Database (SPD): The SPD contains entries of connection endpoints and the action, which should be applied to packets between those endpoints. Possible actions are Discard, Bypass (IPsec processing) and Protect (en- / decrypt). The router effectively has to perform firewall filtering for the entire traffic, when it matches the incoming packets to the connections listed in the SPD. - Security Association Database (SAD): The SAD contains the negotiated security associations (i.e. cryptographic keys, algorithm, etc.) for each (simplex) connection between two endpoints. It needs to be consulted when the SPD query results in "Protect" and an actual IPsec operation has to be performed on the packet.

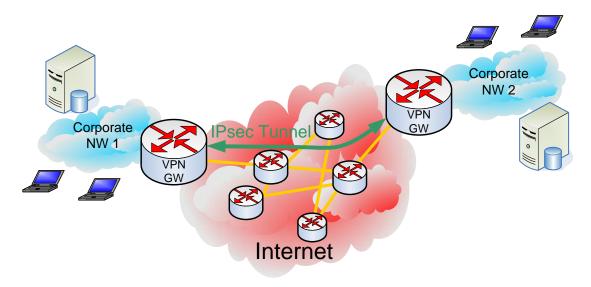

IPsec can be deployed both in the network devices as well as at hosts (i.e. computers). If two hosts protect their communication with IPsec protocols, the routers in the network simply forward those packets, so there are no extra requirements for the NPs in those systems. The more interesting case for the network infrastructure happens, when IPsec protocols are used to establish a secure connection between two sites that are connected over the public Internet (Figure 5). Here, the hosts within the corporate networks (NW1 and NW2) can trust each other and don't have to encrypt their messages. However, as people from one site need to communicate with people from the other site, packets are encrypted by a virtual private network (VPN) gateway router before being released into the public network. Routers in the Internet can only read the outer packet headers going from VPN GW NW1 to VPN GW NW2, but cannot gain any information about the actual communication partners or the contents of the communication.

Figure 5: Confidential Data Transmission with IPsec Tunnel

Depending on the communication bandwidth between the two sites, en- and decryption of the aggregate traffic between the two sites may represent a significant processing burden for the gateway routers, which may not be handled by software processing alone, but is often handled by hardware accelerators (see also the Netronome NFP3200 [21] or SafeNet EIP-196 [19]).

Another application that uses cryptography is the domain of wireless LANs (WLAN). Due to the open nature of the wireless radio link in contrast to wireline links, all communications between the end user device and the WLAN hot spot can be

overheard by anyone without the use of cryptographic methods. Therefore the IEEE WLAN standards have published schemes like wired equivalent privacy (WEP) or Wi-Fi Protected Access (WPA) to better protect wireless networks from attacks. For the same security concerns, the digital radio channels of both GSM and UMTS mobile communication systems feature encryption technology in order to insure confidentiality of the transported information.

## 2.2.4. Multimedia Applications

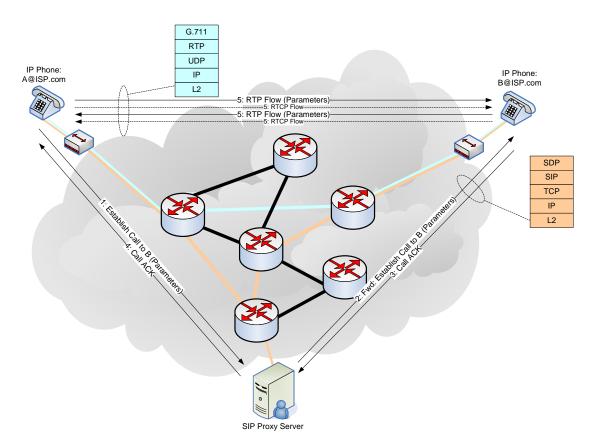

With the increasing availability of high-bandwidth packet data networks, transmission of voice and video data over Internet networks became feasible. The fact, that transmission via packet switched networks is offered for a lower price together with potential cost savings by consolidating voice and data traffic into a single network infrastructure posed another incentive for companies to push for a converged network. In 2003, the IETF released two standards that describe the RTP/RTCP [40] protocols and mappings for voice and video data into RTP streams [41] to allow for transmission of voice and video streams over classical IP networks. RTP is typically used on top of UDP to provide sequence numbers and time stamps for the otherwise unprotected datagram delivery protocol. Transmission of real-time data using the TCP protocol that already insures correct packet sequence at Layer 4 is not advisable, as the delays caused by the TCP protocol e.g. in case of packet loss or reordering is not acceptable for interactive communication. However, the RTP/RTCP protocols alone are not sufficient to implement a voice-over-IP (VoIP) system [42], as it contains no signaling protocol. For this purpose, protocols like session initiation protocol (SIP) [43], [44] or H.323 have to be used. These protocols negotiate the call parameters between two or more endpoints (e.g. used codec, port numbers for RTP and RTCP connection for both directions, bandwidth reservations, etc.) before the actual RTP connection can be established to transport the digitized voice samples in an appropriate format (see Figure 6). Apart from the communication via SIP/RTP protocols, commercial VoIP providers like, for example, Skype have also developed their own, proprietary protocols to achieve IP-based telephony services.

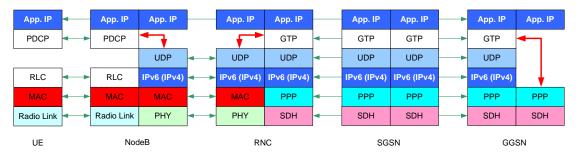

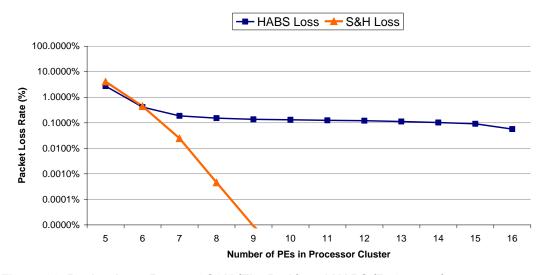

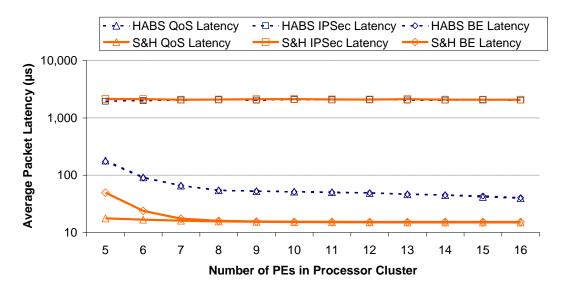

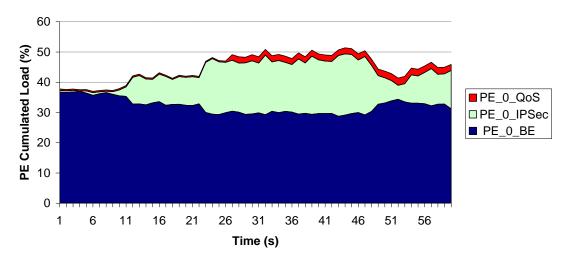

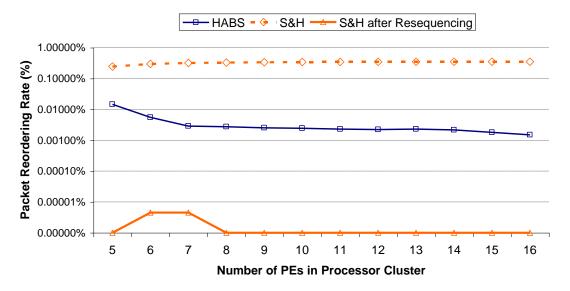

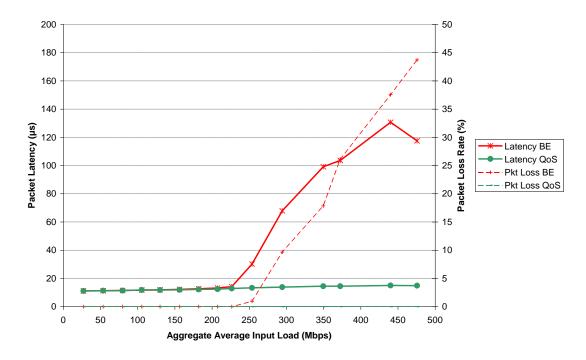

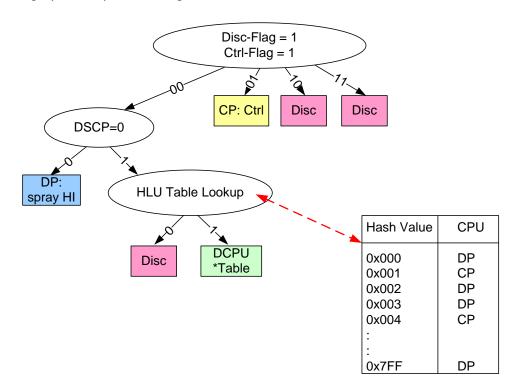

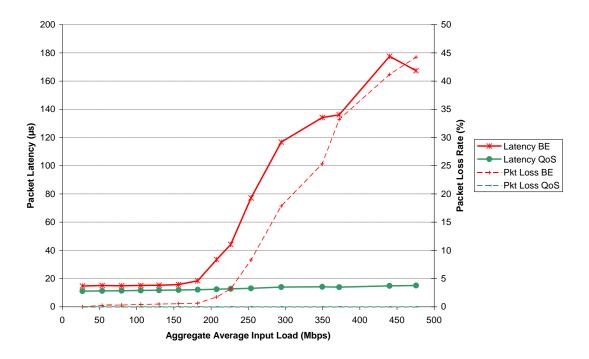

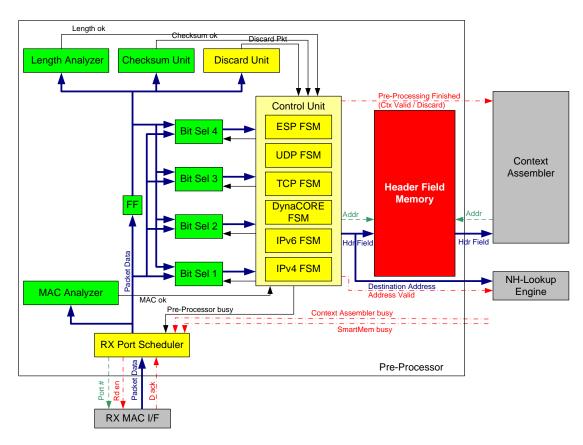

Figure 6: Simplified Connection Setup and Protocol Stack for VoIP